# **Dual Output Power Supply with Positive/Negative Voltage**

#### **Features**

- Split-rail power supply

- Input voltage range: 2.7 V to 5.5 V

- Under voltage lockout rising/falling

- Programmable output voltage

- Positive output voltage range:

4 V to 6 V (0.1 V step)

- Negative output voltage range:

-4 V to -6 V (0.1 V step)

- ±1% output voltage accuracy

- Programmable active discharge

- Excellent line regulation

- Advanced power-save mode for light-load efficiency

- Thermal shutdown

- WLCSP-15 package

## **Applications**

- TFT LCD smart phones, tablets

- OLED displays

- General dual power supply applications

- Operational amplifier supply (including audio)

- DAC supply

## **Descriptions**

The DIO5639 is designed to support general positive/negative driven applications. The device uses a single inductor scheme in order to provide the user with the smallest solution size possible as well as high efficiency. With its input voltage range of 2.7 V to 5.5 V, it is optimized for products powered by single-cell batteries (Li-ion, Ni-Li, Li-Polymer) and output currents up to 280 mA. After I<sup>2</sup>C programming internal registers, the data can keep unchanged even if ENN and ENP disable the device when the device is powered. The device is delivered in a WLCSP-15 package.

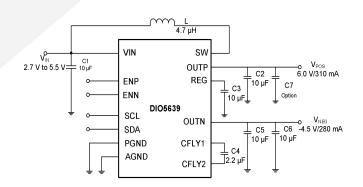

## **Typical Application**

## **Ordering Information**

| Or | der Part Number | Top Marking | RoHS  | T <sub>A</sub> | Pa       | ıckage            |

|----|-----------------|-------------|-------|----------------|----------|-------------------|

|    | DIO5639WL15     | 5639        | Green | -40 to 85°C    | WLCSP-15 | Tape & Reel, 3000 |

More P/N version details please refer to Device Comparison Table.

**Device Comparison Table**

| <b>5</b> (N) | Default                                               |                   |                                    | Startup Time                           |                 |          |

|--------------|-------------------------------------------------------|-------------------|------------------------------------|----------------------------------------|-----------------|----------|

| Part Number  | Output<br>Voltages                                    | Output<br>Current | Active<br>Discharge <sup>(1)</sup> | V <sub>POS</sub> /V <sub>NEG</sub> (2) | I <sub>SD</sub> | Package  |

| DIO5639      | V <sub>POS</sub> = 6.0 V<br>V <sub>NEG</sub> = -4.5 V | 280 mA            | V <sub>POS</sub> /V <sub>NEG</sub> | SLOW                                   | 35 uA           | WLCSP-15 |

<sup>(1)</sup> See "Power-Down And Discharge(LDO)" and "Power-Down and Discharge (CPN)" for a detailed description of how each device variant implements the active discharge function.

(2) See "Power-Up And Soft-Start (LDO)" and "Power-Up And Soft-Start (CPN)" for more details.

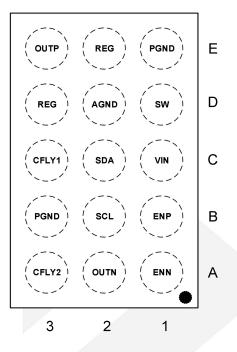

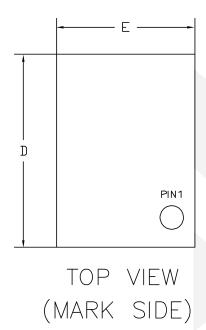

## **Pin Assignments**

WLCSP-15

Figure 1. Pin Assignment

## **Pin Definitions**

| PIN   | I/O | Description                                                |

|-------|-----|------------------------------------------------------------|

| AGND  | -   | Analog ground                                              |

| CFLY1 | I/O | Negative charge pump flying capacitor pin                  |

| CFLY2 | I/O | Negative charge pump flying capacitor pin                  |

| ENN   | 1   | Enable pin for V <sub>NEG</sub> rail                       |

| ENP   | ı   | Enable pin for V <sub>POS</sub> rail                       |

| OUTP  | 0   | Output pin of the LDO (V <sub>POS</sub> )                  |

| OUTN  | 0   | Output pin of the negative charge pump (V <sub>NEG</sub> ) |

| PGND  | -   | Power ground                                               |

| REG   | 1/0 | Boost converter output pin                                 |

| SCL   | I/O | I <sup>2</sup> C interface clock signal pin                |

| SDA   | I/O | I²C interface data signal pin                              |

| sw    | I/O | Switch pin of the boost converter                          |

| VIN   | I   | Input voltage supply pin                                   |

## **Absolute Maximum Ratings**

Stresses beyond those listed under the Absolute Maximum Rating table may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Para                               | Rating     | Unit |   |

|------------------------------------|------------|------|---|

| Voltage range on CFLY1, ENN, ENP,  | -0.3 to 7  | V    |   |

| Voltage range on CFLY2, OUTN       | -7 to 0.3  | V    |   |

| Operating temperature range.       | -40 to 85  | °C   |   |

| Junction temperature range         | -40 to 150 | °C   |   |

| Package thermal resistance WLCSP-  | 76.5       | °C/W |   |

| Storage temperature                | -65 to 150 | °C   |   |

| Lead temperature (soldering, 10 s) | 260        | °C   |   |

| ESD susceptibility HBM             |            | 2000 | V |

## **Recommend Operating Conditions**

Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. DIOO does not recommend exceeding them or designing to absolute maximum ratings.

| Parameter                           | Rating     | Unit |

|-------------------------------------|------------|------|

| Input voltage range                 | 2.7 to 5.5 | V    |

| Inductor                            | 2.2 to 4.7 | μН   |

| Input capacitor <sup>(1)(2)</sup>   | 4.7 to 10  | μF   |

| Fly capacitor <sup>(1)(2)</sup>     | 2.2 to 4.7 | μF   |

| Output capacitors <sup>(1)(2)</sup> | 4.7 to 20  | μF   |

| Junction temperature range          | -40 to 125 | °C   |

| Ambient temperature range           | -40 to 85  | °C   |

- (1) Please see Detailed Description section for further information.

- (2) X7R (or better dielectric material) is recommended.

## **Electrical Characteristics**

$T_A$  = 25°C,  $V_{IN}$  = 3.7 V, ENN = ENP =  $V_{IN}$ ,  $V_{POS}$  = 6.0 V,  $V_{NEG}$  = -4.5 V, unless otherwise specified.

| Symbol                | Parameter                            | Test Conditions                                                             | Min | Тур  | Max | Un |

|-----------------------|--------------------------------------|-----------------------------------------------------------------------------|-----|------|-----|----|

| Supply cui            | rrent                                |                                                                             |     |      |     |    |

| V <sub>IN</sub>       | Input voltage range                  |                                                                             | 2.7 |      | 5.5 | V  |

| V                     | Under voltage lockout threshold      | V <sub>IN</sub> rising                                                      |     |      | 2.5 | V  |

| V <sub>UVLO</sub>     | UVLO delay                           | V <sub>IN</sub> falling                                                     |     |      | 2.3 | V  |

| ΙQ                    | Quiescent current                    | Boost converter and charge pump not switching                               |     | 0.58 |     | m  |

|                       | Thermal shutdown                     |                                                                             |     | 140  |     | °( |

|                       | Thermal shutdown hysteresis          |                                                                             |     | 20   |     | °( |

| ₋ogic ENN             | , ENP, SCL, SDA                      |                                                                             |     |      |     |    |

| V <sub>IH</sub>       | High level input voltage             | V = 2.7 V to 5.5 V                                                          | 1.3 |      |     | \  |

| VIL                   | Low level input voltage              | $V_{IN} = 2.7 \text{ V to } 5.5 \text{ V}$                                  |     |      | 0.4 | \  |

| R <sub>EN</sub>       | ENN, ENP pulldown resistors          |                                                                             |     | 200  |     | k! |

| Boost con             | verter                               |                                                                             |     |      |     |    |

| I <sub>LIM</sub>      | Boost converter valley current limit |                                                                             |     | 1.2  |     | A  |

| f <sub>SW</sub>       | Boost converter switching frequency  |                                                                             |     | 1.5  |     | MI |

| ₋DO outpu             | it V <sub>POS</sub>                  |                                                                             |     |      |     |    |

| $V_{\text{POS}}$      | Positive output voltage range        |                                                                             | 4   |      | 6   | \  |

| $V_{\text{POS\_acc}}$ | Positive output voltage accuracy     |                                                                             | -1  |      | 1   | 9/ |

| I <sub>POS</sub>      | Positive output current capability   | V <sub>POS</sub> drop to 95%                                                | 310 |      |     | m  |

| $V_{DO}$              | Dropout voltage                      | V <sub>REG</sub> = V <sub>POS(NOM)</sub> = 5.4 V, I <sub>OUT</sub> = 200 mA |     | 50   |     | m  |

|                       | Line regulation                      | V <sub>IN</sub> = 2.7 V to 5.5 V, I <sub>OUT</sub> = 200 mA                 |     | 0.5  |     | %  |

|                       | Load regulation                      | Δl <sub>OUT</sub> = 200 mA                                                  |     | 3    |     | %/ |

| R <sub>D</sub>        | Discharge resistor                   | Factory programmable: 15, 20, 30, 70                                        |     | 70   |     | Ω  |

| Tss                   | Soft-start time                      | Factory programmable to be slow or fast                                     |     | 0.60 |     | m  |

| V <sub>NEG</sub>     | Negative output voltage range            |                                                             | -4.0 |     | -6.0 | V   |

|----------------------|------------------------------------------|-------------------------------------------------------------|------|-----|------|-----|

| V <sub>NEG_acc</sub> | Negative output voltage accuracy         |                                                             | -1   |     | 1    | %   |

|                      | Nonetice autout account and bility       | Smartphone MODE                                             | 80   |     |      | mA  |

| I <sub>NEG</sub>     | Negative output current capability       | Tablet MODE                                                 | 280  |     |      | mA  |

| fosc                 | Negative charge pump switching frequency |                                                             |      | 1.0 |      | MHz |

|                      | Line regulation                          | V <sub>IN</sub> = 2.7 V to 5.5 V, I <sub>OUT</sub> = 150 mA |      | 0.5 | 1    | %   |

|                      | Load regulation                          | ΔI <sub>OUT</sub> = 200 mA                                  |      | 5   |      | %/A |

| R <sub>D</sub>       | Discharge resistor                       |                                                             |      | 20  |      | Ω   |

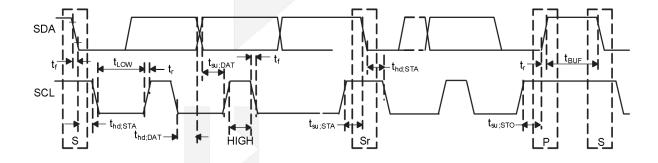

## I<sup>2</sup>C Interface Timing Requirements/Characteristics

| Symbol              | Parameter                                      | Test Conditions | Min  | Тур | Max  | Unit |

|---------------------|------------------------------------------------|-----------------|------|-----|------|------|

|                     | CCL clock fraguency                            | Standard MODE   |      |     | 100  | kHz  |

| fscL                | SCL clock frequency                            | Fast MODE       |      |     | 400  | kHz  |

| t <sub>LOW</sub>    | LOW period of the SCL clock                    | Standard MODE   | 4.7  |     |      | μs   |

| LOW                 | LOW period of the OCL Glock                    | Fast MODE       | 1.3  |     |      | μs   |

| turou               | t <sub>HIGH</sub> HIGH period of the SCL clock | Standard MODE   | 4    |     |      | μs   |

| чісн                |                                                | Fast MODE       | 600  |     |      | ns   |

| t <sub>BUF</sub>    | Bus free time between a STOP                   | Standard MODE   | 4.7  |     |      | μs   |

| TBUF                | and START condition                            | Fast MODE       | 1.3  |     |      | μs   |

| t <sub>hd;STA</sub> | Hold time for a repeated START condition       | Standard MODE   | 4    |     |      | μs   |

| uiu,STA             |                                                | Fast MODE       | 600  |     |      | ns   |

| t <sub>su;STA</sub> | Setup time for a repeated START condition      | Standard MODE   | 4.7  |     |      | μs   |

| tsu;STA             |                                                | Fast MODE       | 600  |     |      | ns   |

| t <sub>su;DAT</sub> | Data setup time                                | Standard MODE   | 250  |     |      | ns   |

| Su,DAI              | Data comp and                                  | Fast MODE       | 100  |     |      | ns   |

| t <sub>hd:DAT</sub> | Data hold time                                 | Standard MODE   | 0.05 |     | 3.45 | μs   |

| GIQ,DAI             | Data floid diffe                               | Fast MODE       | 0.05 |     | 0.9  | μs   |

|                     | Rise time of SCL signal after a                       | Standard MODE | 20 +0.1 CB | 1000 | ns |

|---------------------|-------------------------------------------------------|---------------|------------|------|----|

| t <sub>RCL1</sub>   | repeated START condition and after an acknowledge bit | Fast MODE     | 20 +0.1 CB | 1000 | ns |

| t                   | Disa time of SCI signal                               | Standard MODE | 20 +0.1 CB | 1000 | ns |

| t <sub>RCL</sub>    | Rise time of SCL signal                               | Fast MODE     | 20 +0.1 CB | 300  | ns |

| tea                 | Fall time                                             | Standard MODE | 20 +0.1 CB | 300  | ns |

| t <sub>FCL</sub>    | raii ume                                              | Fast MODE     | 20 +0.1 CB | 300  | ns |

|                     | Rise time of SDA signal                               | Standard MODE | 20 +0.1 CB | 1000 | ns |

| t <sub>RDA</sub>    |                                                       | Fast MODE     | 20 +0.1 CB | 300  | ns |

| t <sub>FDA</sub>    | Fall time of SDA signal                               | Standard MODE | 20 +0.1 CB | 300  | ns |

| LFDA                | Fall time of SDA signal                               | Fast MODE     | 20 +0.1 CB | 300  | ns |

| t ===               | Setup time for STOP condition                         | Standard MODE | 4          |      | μs |

| t <sub>su;STO</sub> | Setup time for 310F condition                         | Fast MODE     | 600        |      | ns |

| Св                  | Capacitive load for SDA and SCL                       |               |            | 0.4  | nF |

Specifications subject to change without notice.

Figure 2. Serial Interface Timing For F/S-Mode

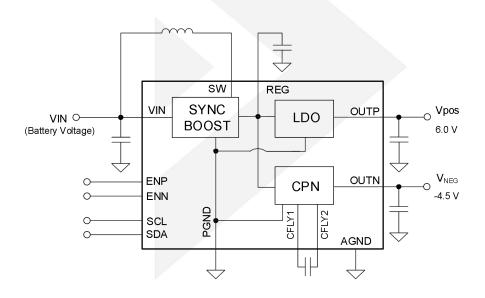

## **Detailed Description**

#### 1. Overview

The DIO5639, supporting input voltage from 2.7 V to 5.5 V, operates with a single inductor scheme to provide a high efficiency with a small solution size. The synchronous boost converter generates a positive voltage that is regulated down by an integrated LDO, providing the positive supply rail (V<sub>POS</sub>). The negative supply rail (V<sub>NEG</sub>) is generated by an integrative charge pump (or CPN) driven from the boost converter output pin REG. The operating mode can be selected between Smartphone and Tablet in order to select the necessary output current capability and to get the best efficiency possible based on the application. The device topology allows a 100% asymmetry of the output currents. After I<sup>2</sup>C programming internal registers, the data can keep unchanged even if ENN and ENP disable the device when the device is powered.

#### 2. Functional Block Diagram

Figure 3. Function Block Diagram

#### 3. Feature Description

#### 3.1 Under Voltage Lockout (UVLO)

The DIO5639 integrates an under voltage lockout block (UVLO) that enables the device once the voltage on the VIN pin exceeds the UVLO threshold (2.5 V maximum). No output voltage will however be generated as long as the enable signals are not pulled HIGH. The device, as well as all converters (boost converter, LDO, CPN), will be disabled as soon as the V<sub>IN</sub> voltage falls below the UVLO threshold. The UVLO threshold is designed in a way that the DIO5639 will continue operating as long as V<sub>IN</sub> stays above 2.3 V. This guarantees a proper operation even in the event of extensive line transients when the battery gets suddenly heavily loaded.

For DIO5639, a 40 ms delay is starting as soon as the UVLO threshold is reached. This delay prevents the device to be disabled and enabled by an unwanted VIN voltage spike. Once this delay has passed, the output rails can be enabled as desired with the enable signals without any delay.

#### 3.2 Active Discharge

An active discharge of the positive rail and/or the negative rail can be programmed (DISP and CISN bits respectively – refer to DAC Registers). If programmed to be active, the discharge will occur at power down, when the enable signals go LOW. See "Power-Down And Discharge (LDO)" and "Power-Down And Discharge (CPN)" for a detailed description of how each device variant implements the active discharge function.

### 3.3 Boost Converter

### 3.3.1 Boost Converter Operation

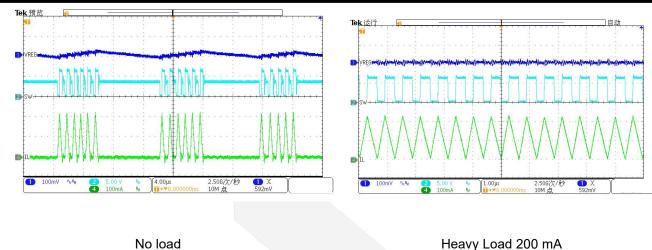

The synchronous boost converter uses a current mode topology and operates at a quasi-fixed frequency of typically 1.5 MHz, allowing chip inductors such as 2.2  $\mu$ H or 4.7  $\mu$ H to be used. The converter is internally compensated and provides a regulated output voltage automatically adjusted depending on the programmed  $V_{POS}$  and  $V_{NEG}$  voltage. The boost converter operates either in continuous conduction mode (CCM) or Pulse Frequency Modulation mode (PFM), depending on the load current in order to provide the highest efficiency possible.

### 3.3.2 Power-Up And Soft-Start (Boost Converter)

The boost converter starts switching as soon as the enable signal is pulled HIGH and the voltage on the VIN pin is above the UVLO threshold. For the DIO5639, in the case where the enable signal is already HIGH when  $V_{IN}$  reaches the UVLO threshold, the boost converter will only start switching after a 40 ms delay has passed.

The boost converter starts up with an integrated soft-start to avoid drawing excessive inrush current from the supply. The output voltage V<sub>REG</sub> is slowly ramped up to its target value.

### 3.3.3 Power-Down (Boost Converter)

The boost converter stops switching when  $V_{IN}$  is below the UVLO threshold or when both output rails are disabled. For example, due to a special sequencing, the LDO might still be operating while the CPN is already disabled, in which case, the boost will continue operating until the LDO has been disabled.

### 3.3.4 Isolation (Boost Converter)

The boost converter output (REG) is isolated from the input supply  $V_{IN}$ , providing a true shutdown.

#### 3.3.5 Output Voltage (Boost Converter)

The output voltage of the boost converter is automatically adjusted depending on the programmed  $V_{POS}$  and  $V_{NEG}$  voltage.

#### 3.3.6 Advanced Power-Save Mode For Light-Load Efficiency And PFM

The DIO5639 device integrates a power save mode to improve efficiency at light load. In power save mode the converter stops switching when the inductor current reaches 0 A. The device resumes its switching activity with one or more pulses once the V<sub>REG</sub> voltage falls below its regulation level, and goes again into power save mode once the inductor current reaches 0 A. The pulse duration remains constant, but the frequency of these pulses varies according to the output load. This operating mode is also known as Pulse Frequency Modulation or PFM.

### 3.4 LDO Regulator

### 3.4.1 LDO Operation

The Low Dropout regulator (or LDO) generates the positive voltage rail  $V_{POS}$  by regulating down the output voltage of the boost converter ( $V_{REG}$ ). Its inherent power supply rejection helps filter the output ripple of the boost converter in order to provide on OUTP pin a clean voltage, e.g. to supply the source driver IC of the display.

### 3.4.2 Power-Up And Soft-Start (LDO)

The LDO starts operating as soon as the ENP signal is pulled HIGH, the  $V_{IN}$  voltage is above the UVLO threshold and the boost converter has reached its Power Good threshold.

In the case where the enable signal is already HIGH when  $V_{IN}$  exceeds the UVLO threshold, the boost converter will start first and the LDO will only start after the boost converter has reached its target voltage. For the DIO5639 the boost will start after the 40 ms delay has passed.

The LDO integrates a soft-start that slowly ramps up its output voltage VPOS regardless of the output capacitor, and the target voltage, as long as the LDO current limit is not reached. For DIO5639 the typical startup time is 600 µs.

### 3.4.3 Power-Down And Discharge (LDO)

The LDO stops operating when  $V_{IN}$  is below the UVLO threshold or when ENP is pulled LOW.

The positive rail can be actively discharged to GND during power-down if required. A discharge selection bit is available to enable or disable this function. See the table below for more details.

| Table 1. | <b>V<sub>POS</sub> Active</b> | Discharge | Behavior |

|----------|-------------------------------|-----------|----------|

|----------|-------------------------------|-----------|----------|

| Part Number | V <sub>IN</sub>     | ENP        | ENN        | V <sub>POS</sub> Discharge |

|-------------|---------------------|------------|------------|----------------------------|

|             | < V <sub>UVLO</sub> | Don't care | Don't care | On                         |

|             |                     | Low        | Low        | On                         |

| DIO5639     |                     | Low        | High       | Determined by DISP bit     |

|             | > V <sub>UVLO</sub> | High       | Low        | Off                        |

|             |                     | High       | High       | Off                        |

### 3.4.4 Isolation (LDO)

The LDO is isolating the  $V_{POS}$  rail from  $V_{REG}$  (boost converter output) as long as the rail is not enabled in order to ensure flexible startup like  $V_{NEG}$  before  $V_{POS}$ .

### 3.4.5 Setting the output voltage (LDO)

The output voltage of the LDO is programmable via an I<sup>2</sup>C compatible interface, from -4.0 V to -6.0 V with 100 mV steps. For more details, please refer to the DAC settings section.

### 3.5 Negative Charge Pump

### 3.5.1 Operation

The negative charge pump (CPN) generates the negative voltage rail  $V_{NEG}$  by inverting and regulating the output voltage of the boost converter ( $V_{REG}$ ). The charge pump uses 4 switches and an external flying capacitor to generate the negative rail. Two of the switches are turned on in the first phase to charge the flying capacitor up to  $V_{REG}$ , and in the second phase they are turned off and the two others turn on to pump the energy negatively out of the OUTN capacitor.

### 3.5.2 Power-up and soft-start (CPN)

The CPN starts operating as soon as the ENN signal is pulled HIGH, the  $V_{IN}$  voltage is above the UVLO threshold and the boost converter has reached its Power Good threshold.

In the case where the enable signal is already HIGH when VIN reaches the UVLO threshold, the boost converter will start first and the CPN will only start after the boost converter has reached its target voltage. For the DIO5639, the boost will start after the 40 ms delay has passed.

### 3.5.3 Power-down and discharge (CPN)

The CPN stops operating when V<sub>IN</sub> is below the UVLO threshold or when ENN is pulled LOW.

The negative rail can be actively discharged to GND during power-down if required. A discharge selection bit is available to enable or disable this function. See the table below for more details.

### Table 2. V<sub>NEG</sub> active discharge behavior

| Part Number | V <sub>IN</sub>     | ENP        | ENN        | V <sub>NEG</sub> DISCHARGE |

|-------------|---------------------|------------|------------|----------------------------|

|             | < V <sub>UVLO</sub> | Don't care | Don't care | On                         |

|             | > V <sub>UVLO</sub> | Low        | Low        | On                         |

| DIO5639     |                     | Low        | High       | Off                        |

|             |                     | High       | Low        | Determined by DISN bit     |

|             |                     | High       | High       | Off                        |

### 3.5.4 Isolation (CPN)

The CPN isolates the  $V_{NEG}$  rail from  $V_{REG}$  (boost converter output) as long as the rail is not enabled in order to ensure flexible startup like  $V_{POS}$  before  $V_{NEG}$ .

### 3.5.5 Setting the output voltage (CPN)

The output voltage of the CPN is programmable via an I<sup>2</sup>C compatible interface, from -4.0 V to -6.0 V with 100 mV steps. For more details, please refer to the DAC settings section.

#### 3.6 Simultaneous On/Off control of LDO and CPN

When the control bit of "SEQD" is set to high (see DAC setting table), LDO and CPN will start up and shut down simultaneously and they are controlled by ENN ORing ENP, which means either ENN or ENP is high will enable both LDO and CPN while both ENN and ENP are low will disables LDO and CPN. This feature gives flexibility for the customer to control the sequence to LDO and CPN.

### 4. Device Functional Mode

#### 4.1 Enabling and disabling the device

The DIO5639 is enabled as long as the VIN voltage is above the UVLO and one of the enable pins (ENP or ENN) is HIGH. Pulling ENP or ENN LOW disables either rail (V<sub>POS</sub> or V<sub>NEG</sub> respectively); and, pulling both pins LOW disables the device entirely (the internal oscillator of the DIO5639 continues running to allow access to the I<sup>2</sup>C interface)

#### 5. Programming

### 5.1 I<sup>2</sup>C serial interface description

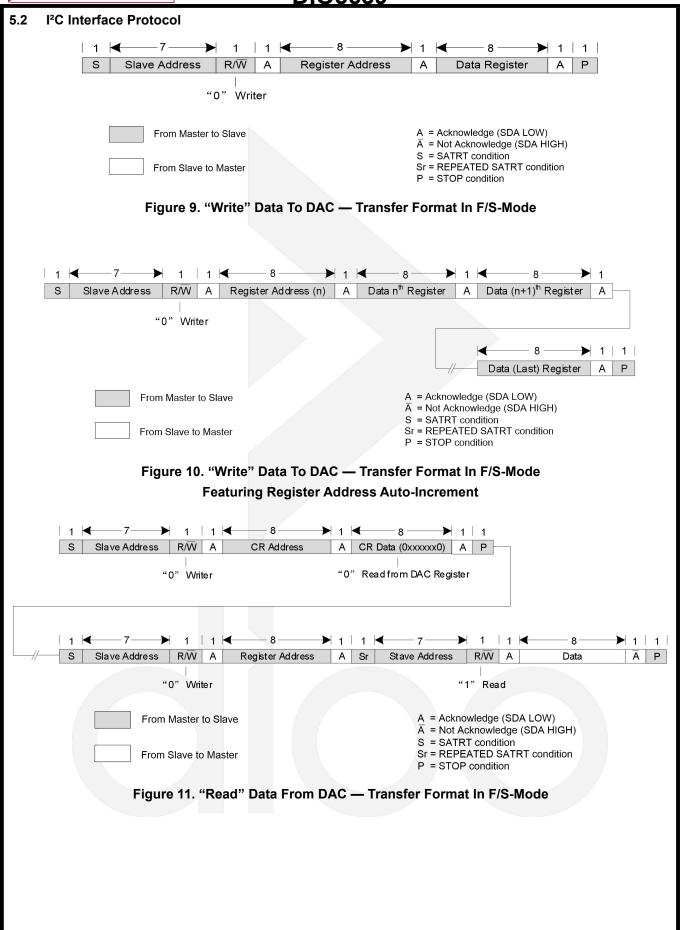

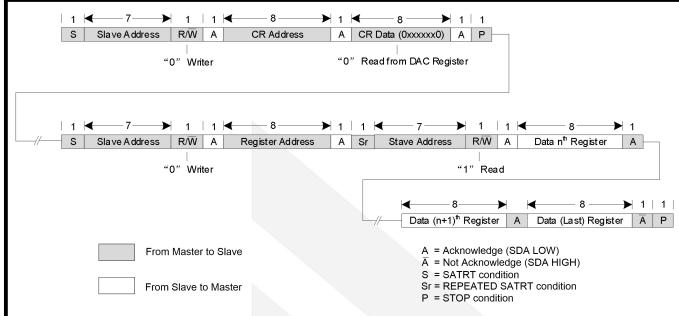

The DIO5639 communicates through an industry-standard I<sup>2</sup>C compatible interface, to receive data in slave mode.

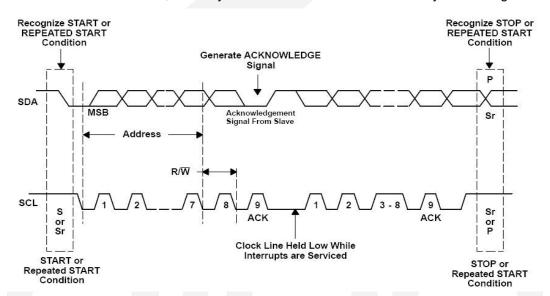

The bus consists of a data line (SDA) and a clock line (SCL) with pull-up structures. A master device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A slave device receives and/or transmits data on the bus under the control of the master device.

The DIO5639 works as a slave and supports the following data transfer modes, as defined in the I<sup>2</sup>C-Bus specification: standard mode (100 kbps) and fast mode (400 kbps). The data transfer protocol for standard and

fast modes is exactly the same, therefore they are referred to as F/S-mode in this document. The DIO5639 supports 7-bit addressing. The device 7-bit address is 3E, and the LSB enables the write or read function.

| MSB                      | DIO5 | 639 | Address |   |   |   | LSB |

|--------------------------|------|-----|---------|---|---|---|-----|

| 0                        | 1    | 1   | 1       | 1 | 1 | 0 | R/W |

| $R/\overline{W} = R/(W)$ |      |     |         |   |   |   |     |

Figure 4. DIO5639 Slave address byte

The device that initiates the communication is called a master, and the devices controlled by the master are slaves. The master generates the serial clock on SCL, controls the bus access, and generates START and STOP conditions. A START initiates a new data transfer to a slave. Transitioning SDA from high to low while SCL remains high generates a START condition. A STOP condition ends a data transfer to a slave. Transitioning SDA from low to high while SCL remains high generates a STOP condition.

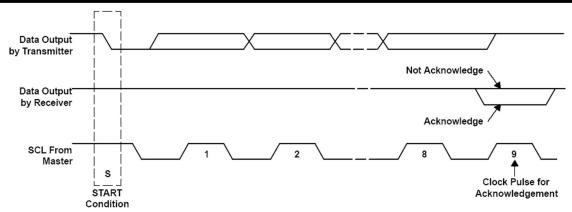

Figure 5. Start And Stop Conditions

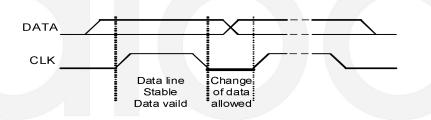

The master then generates the SCL pulses and transmits the 7-bit address and the read/write direction bit R/(W) on the SDA line. During all transmissions, the master ensures that the data is valid. A valid data condition requires the SDA line to be stable during the entire high period of the clock pulse. All devices recognize the address sent by the master and compare it to their internal fixed addresses. Compare only the slave device with a matching address sent by the master to their internal fixed addresses. Only the slave device with a matching address generates an Acknowledgment, ACK, by pulling the SDA line low during the entire high period of the SCL cycle. Upon detecting this Acknowledgment, the master knows that a communication link with a slave has been established.

Figure 6. Bit Transfer on The Serial Interface

Figure 7. Acknowledge On The IC Bus<sup>2</sup>

The master generates further SCL cycles to either transmit data to the slave (R/(W) bit = 0) or receive data from the slave (R/(W) bit = 1). In either case, the receiver needs to acknowledge the data sent by the transmitter. So an acknowledge signal can either be generated by the master or by the slave, depending on which one is the receiver. 9-bit valid data sequences consisting of 8-bit data and 1-bit acknowledge can continue as long as necessary. To terminate the data transfer, the master generates a STOP condition by pulling the SDA line from low to high while the SCL line is high. This releases the bus and stops the communication link with the addresses slave. All I²C compatible devices must recognize the bus and stops the communication link with the addressed slave. All I²C compatible devices must recognize the stop condition. Upon the receipt of a stop condition, all devices know that the bus is released, and they wait for a start condition followed by a matching address.

Figure 8. Bus Protocol

Figure 12. "Read" Data From DAC — Transfer Format In F/S-Mode Featuring Register Address Auto-Increment

## 6. Register Map

The DIO5639 has one non-volatile memory which contains the initial value of the DAC and one volatile memory which contains the DAC setting. The non-volatile memory is called the Initial Value Register (IVR) and the volatile memory is called DAC Register (DR). The non-volatile IVR and the volatile memory is called DAC Register (DR). The non-volatile IVR and the volatile DR are accessed with the same address.

**Start option**: At power-up, the value contained in the IVR is loaded into the volatile DR and IVR presets the DAC to the last stored setting within less than 20 µs. The programmed factory value if IVR of each address is described below and, at power-up, these data byte set the output voltage of each rail.

Slave address: 0x3E

X=R/W = 1→read mode

R/W = 0→write mode

#### 6.1 DAC Registers

| Bit7 | Bit6 | Bit5 | Bit4      | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|-----------|------|------|------|------|

| RSVD | RSVD | RSVD | VPOS[4:0] |      |      |      |      |

|      | R    |      | R/W       |      |      |      |      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### Figure 13. VPOS Register - 0x00

| Bit7 | Bit6 | Bit5 | Bit4      | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|-----------|------|------|------|------|

| RSVD | RSVD | RSVD | VNEG[4:0] |      |      |      |      |

| R    |      |      | R/W       |      |      |      |      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Figure 14. VNEG Register - 0x01

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| RSVD | APPS | RSVD | RSVD | RSVD | SEQD | DISP | DISN |

| R    | R/W  | R    | R    | R    | R/W  | R/W  | R/W  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Figure 15. APPS - DISP - DISN Register - 0x03

(1) See Power-Down And Discharge (LDO) and Power-Down And Discharge (CPN) for a detailed description of how each device variant implements the active discharge function.

The Reserved bits are ignored when written and return either 0 or 1 when read.

Attempting to read data from register addresses not listed in the following section will result in 0x00 being read out.

### 6.2 DAC Settings

The following tables show the DAC values and the corresponding voltages of each block address.

| VPOS-0x00 | VPOS  | VNEG-0x01 | VNEG   | APPS-0x03 | APPLICATION                          |

|-----------|-------|-----------|--------|-----------|--------------------------------------|

| 00h       | 4.0 V | 00h       | -4.0 V | 0         | Smartphone                           |

| 01h       | 4.1 V | 01h       | -4.1 V | 1         | Tablet                               |

| 02h       | 4.2 V | 02h       | -4.2 V |           |                                      |

| 03h       | 4.3 V | 03h       | -4.3 V |           |                                      |

| 04h       | 4.4 V | 04h       | -4.4 V |           |                                      |

| 05h       | 4.5 V | 05h       | -4.5 V | DISP-0x03 | LDO ACTIVE DISCHARGE                 |

| 06h       | 4.6 V | 06h       | -4.6 V | 0         | No discharge                         |

| 07h       | 4.7 V | 07h       | –4.7 V | 1         | V <sub>POS</sub> actively discharged |

| 08h       | 4.8 V | 08h       | -4.8 V |           |                                      |

| 09h       | 4.9 V | 09h       | -4.9 V |           |                                      |

| 0Ah       | 5.0 V | 0Ah       | -5.0 V | DISN-0x03 | CPN ACTIVE DISCHARGE                 |

| 0Bh       | 5.1 V | 0Bh       | –5.1 V | 0         | No discharge                         |

| 0Ch       | 5.2 V | 0Ch       | -5.2 V | 1         | V <sub>NEG</sub> actively discharged |

| 0Dh       | 5.3 V | 0Dh       | -5.3 V |           |                                      |

| 0Eh       | 5.4 V | 0Eh       | -5.4 V | SEQD-0x03 | SIMULTANEOUS MODE                    |

| 0Fh       | 5.5 V | 0Fh       | -5.5 V | 0         | Sequence mode                        |

| 10h       | 5.6 V | 10h       | -5.6 V | 1         | Simultaneous mode                    |

| 11h       | 5.7 V | 11h       | –5.7 V |           |                                      |

| 12h       | 5.8 V | 12h       | -5.8 V |           |                                      |

| 13h       | 5.9 V | 13h       | -5.9 V |           |                                      |

| 14h       | 6.0 V | 14h       | -6.0 V |           |                                      |

#### 6.3 Factory Default Register Value

| Dout mumber | Register address |      |      |      |  |

|-------------|------------------|------|------|------|--|

| Part number | 0×00             | 0x01 | 0x02 | 0x03 |  |

| DIO5639     | 0x14             | 0x05 | _    | 0x43 |  |

### 7. Application and Implementation

## 7.1 Application Information

The DIO5639 devices, primarily intended to supplying TFT LCD displays, can be used for any application that requires positive and negative supplies, ranging from ±4 V to ±6 V and current up to 280 mA. Both output voltages can be set independently and their sequencing is also independent. The following section presents the different operating modes that the device can support as well as the different features that user can select.

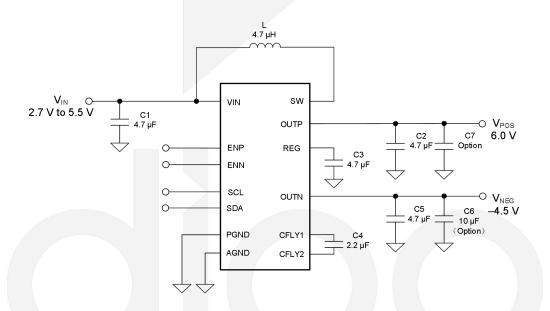

### 7.2 Typical Applications

### 7.2.1 Low-current Applications (≤ 80 mA)

The DIO5639 can be programmed to Smartphone mode with the APPS bit to support applications that require output currents up to 80 mA (refer to DAC Settings). The Smartphone mode limits the negative charge pump output current to 80 mA DC in order to provide the highest efficiency possible. The  $V_{POS}$  rail can deliver up to 200 mA DC regardless of the mode. Output peak currents are supported by the output capacitors.

Figure 16. Typical Application Circuit For Smart phones

#### 7.2.1.1 Design Requirements

| PARMETERS                                | EXAMPLE VALUES |  |  |

|------------------------------------------|----------------|--|--|

| Input voltage range                      | 2.7 V to 5.5 V |  |  |

| Output voltage                           | 4.0 V to 6.0 V |  |  |

| Output current rating                    | 80 mA          |  |  |

| Boost converter switching frequency      | 1.5 MHz        |  |  |

| Negative charge pump switching frequency | 1.0 MHz        |  |  |

### 7.2.1.2 Detailed Design Procedure

### Sequencing

Each output rail ( $V_{POS}$  and  $V_{NEG}$ ) is enabled and disabled using an external enable signal. If not explicitly specified, the enable signal in the rest of the document refers to ENN or ENP: ENP for positive rail  $V_{POS}$  and ENN for the negative rail  $V_{NEG}$ . In the case where  $V_{IN}$  falls below the UVLO threshold while one of the enable signals is still high, all converters will be shut down instantaneously and both  $V_{POS}$  and  $V_{NEG}$  output rails will be actively discharged to GND.

### **Boost Converter Design Procedure**

The first step in the design procedure is to verify whether the maximum possible output current of the boost converter supports the specific application requirements. A simple approach is to estimate the converter efficiency, by taking the efficiency number from the provided efficiency curves at the application's maximum load or to use a worst-case assumption for the expected efficiency, e.g., 85%.

1. Duty cycle:

$$D = 1 - \frac{V_{IN\_min} \times \eta}{V_{REG}}$$

2. Inductor ripple current:

$$\Delta I_L = \frac{V_{IN\_min} \times D}{f_{SW} \times L}$$

3. Maximum output current:

$$I_{OUT\_max} = (I_{LIM\_min} - \frac{\Delta I_L}{2}) \times (1 - D)$$

4. Peak switch current of the application:

$$I_{SWPEAK} = \frac{I_{OUT}}{1 - V_{REG}} + \frac{\Delta I_L}{2}$$

$\eta$  = Estimated boost converter efficiency (use the number from the efficiency plots or 85% as an estimation)

f<sub>SW</sub> = Boost converter switching frequency (1.5 MHz)

L = Selected inductor value for the boost converter (see the Inductor Selection section)

$I_{SWPEAK}$  = Boost converter switch current at the desired output current (must be < [ $I_{LIM\ min}$  +  $\Delta I_{L}$ ])

$\Delta I_{L}$  = Inductor peak-to-peak ripple current

$V_{REG}$  = Max ( $V_{POS}$ ,  $|V_{NEG}|$ ) + 300 mV (in Smartphone mode — + 400 mV in Tablet mode)

I<sub>OUT</sub> = I<sub>OUT</sub> V<sub>POS</sub> + | I<sub>OUT</sub> V<sub>NEG</sub> | (I<sub>OUT</sub> max being the maximum current delivered on each rail)

The peak switch current is the current that the integrated switch and the inductor have to handle. The calculation must be done for the minimum input voltage where the peak switch current is the highest.

#### Inductor Selection (Boost Converter)

Saturation current: the inductor must handle the maximum peak current ( $I_{L,SAT} > I_{SWPEAK}$ , or  $I_{L,SAT} > [I_{L,M,min} + \Delta I_{L}]$  as conservative approach).

DC Resistance: the lower the DCR, the lower the losses.

Inductor value: in order to keep the ratio  $I_{OUT}/\Delta I_L$  low enough for proper sensing operation purposes, it is recommended to use a 4.7  $\mu$ H inductor for Smartphone mode (a 2.2  $\mu$ H might however be used, but the efficiency might be lower than with 4.7 $\mu$ H at light output loads depending on the inductor characteristics).

### Input Capacitor Selection (Boost Converter)

For best input voltage filtering low ESR ceramic capacitors are recommended. DIO5639 has an analog input pin VIN. A 4.7 µF minimum bypass capacitor is required as close as possible from VIN to GND. This capacitor is also used as the boost converter input capacitor.

For better input voltage filtering, this value can be increased or two capacitors can be used: one 10  $\mu$ F input capacitor for the boost converter as well as a  $1\mu$ F bypass capacitor close to the VIN pin.

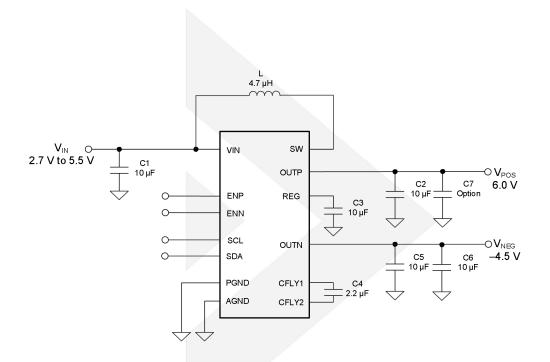

### **Output Capacitor Selection (Boost Converter)**

For the best output voltage filtering, low-ESR ceramic capacitors are recommended. A minimum of 4.7  $\mu$ F(10  $\mu$ F for tablet mode) ceramic output capacitor is required. Higher capacitor values can be used to improve the load transient response.

#### Input Capacitor Selection (LDO)

The LDO input capacitor is also the boost converter output capacitor.

### **Output Capacitor Selection (LDO)**

The LDO is designed to operate with a 4.7  $\mu\text{F}$  minimum ceramic output capacitor.

### Input Capacitor Selection (CPN)

The CPN input capacitor is also the boost converter output capacitor.

#### **Output Capacitor Selection (CPN)**

The CPN is designed to operate with a 4.7 µF minimum ceramic output capacitor.

#### Flying Capacitor Selection (CPN)

The CPN needs an external flying capacitor. The minimum value is 2.2  $\mu$ F for smartphone mode (4.7  $\mu$ F for tablet mode). Special care must be taken while choosing the flying capacitor as it will directly impact the output voltage accuracy and load regulation performance. Therefore, a minimum capacitance of 1  $\mu$ F must be achieved by the capacitor at a DC bias voltage of  $|V_{NEG}|+300$  mV. For proper operation, the flying capacitor value must be lower than the output capacitor of the boost converter on the REG pin.

#### 7.2.1.3 High-current Applications (≤ 280 mA)

The DIO5639 version allows  $V_{POS}$  output currents up to 310 mA and  $V_{NEG}$  output currents up to 280 mA. The DIO5639 can be programmed to Smartphone or Tablet mode with the APPS bit to lower the output current capability of the  $V_{NEG}$  rail if needed (in the case the efficiency is an important parameter).

Figure 17. Typical Application Circuit for Tablet MODE

### 8. Power Supply Recommendations

The devices are designed to operate from an input voltage supply range between 2.7 V and 5.5 V. This input supply must be well-regulated. A ceramic input capacitor with a value of 10  $\mu$ F is a typical choice.

### 8.1 Inductor Selection (Boost Converter)

Saturation current: the inductor must handle the maximum peak current ( $I_{L\_SAT} > I_{SWPEAK}$ , or  $I_{L\_SAT} > [I_{LIM\_min} + \Delta I_{L}]$  as conservative approach)

DC Resistance: the lower the DCR, the lower the losses.

Inductor value: in order to keep the ratio  $I_{OUT}/\Delta I_{L}$  low enough for proper sensing operation purposes, it is recommended to use a 4.7  $\mu$ H inductor for Smartphone mode (a 2.2  $\mu$ H might however be used, but the efficiency might be lower than with 4.7  $\mu$ H at light output loads depending on the inductor characteristics).

**Table 3. Inductor Selection Boost**

| L (µH) | SUPPLIER | COMPONENT CODE     | EIA SIZE | DCR TYP<br>(mΩ) | I <sub>SAT</sub> (A) |

|--------|----------|--------------------|----------|-----------------|----------------------|

| 2.2    | Toko     | 1269AS-H-2R2N = P2 | 1008     | 130             | 2.4                  |

| 2.2    | Murata   | LQM2HPN2R2MG0      | 1008     | 80              | 1.3                  |

| 2.2    | Murata   | LQM21PN2R2NGC      | 0805     | 250             | 0.8                  |

| 4.7    | Toko     | 1269AS-H-4R7N = P2 | 1008     | 250             | 1.6                  |

| 4.7    | Murata   | LQM21PN4R7MGR      | 0805     | 230             | 0.8                  |

| 4.7    | FDK      | MIPS2520D4R7       | 1008     | 280             | 0.7                  |

### 8.2 Capacitor Selection

For best input voltage filtering low ESR ceramic capacitors are recommended. DIO5639 has an analog input pin VIN. A 4.7  $\mu$ F minimum bypass capacitor is required as close as possible from VIN to GND. This capacitor is also used as the boost converter input capacitor.

For better input voltage filtering, this value can be increased or two capacitors can be used: one 4.7 µF input capacitor for the boost converter as well as a 1 µF bypass capacitor close to the VIN pin. Refer to Table 4 for input capacitor recommendations.

For the best output voltage filtering, low-ESR ceramic capacitors are recommended. A minimum of 4.7 μF ceramic output capacitor is required. Higher capacitor values can be used to improve the load transient response. Refer to Table 4 for output capacitor recommendations.

**Table 4. Input And Output Capacitor Selection**

| CAPACITOR (µF) | SUPPLIER | COMPONENT CODE    | EIA SIZE (Thickness max.) | VOLTAGE<br>RATING (V) | COMMENTS                                                                 |

|----------------|----------|-------------------|---------------------------|-----------------------|--------------------------------------------------------------------------|

| 2.2            | Murata   | GRM188R61C225KAAD | 0603 (0.9 mm)             | 16                    | C <sub>FLY</sub>                                                         |

| 4.7            | Murata   | GRM188R61C475KAAJ | 0603 (0.95 mm)            | 16                    | C <sub>IN</sub> , C <sub>NEG</sub> , C <sub>POS</sub> , C <sub>REG</sub> |

| 10             | Murata   | GRM219R61C106KA73 | 0603 (0.95 mm)            | 16                    | C <sub>NEG</sub> , C <sub>REG</sub>                                      |

#### 8.3 Layout Guidelines

PCB layout is an important task in the power supply design. Good PCB layout minimizes EMI and allows very good output voltage regulation. For the DIO5639 the following PCB layout guidelines are recommended.

- Keep the power ground plane on the top layer (all capacitor grounds and PGND pins must be connected together with one uninterrupted ground plane).

- AGND and PGND must be connected together on the same ground plane.

- Place the flying capacitor as close as possible to the IC.

- Always avoid vias when possible. They have high inductance and resistance. If vias are necessary, always

use more than one in parallel to decrease parasitic especially for power lines.

- Connect REG pins together.

- For high dv/dt signals (switch pin trances): keep the copper area to a minimum to prevent making unintentional parallel plate capacitors with other traces or to a ground plane. Best to route the signal and return on the same layer.

- For high di/dt signals: keep traces short, wide, and closely spaced. This will reduce stray inductance and decrease the current loop area to help prevent EMI.

- Keep the input capacitor close to the IC with low inductance traces.

- Keep trace from switching node pin to inductor short if possible: it reduces EMI emission and noise that may couple into other portions of the converter.

- Isolate analog signal paths from power paths.

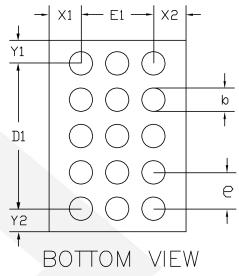

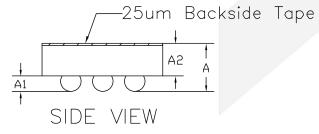

# **Physical Dimensions: WLCSP-15**

BOTTOM VIEW (BALL SIDE)

NOTES: ALL WAFER ORIENTATION NOTCH DOWN

| COMMON DIMENSIONS (MM) |            |            |       |  |  |  |  |

|------------------------|------------|------------|-------|--|--|--|--|

| Symbol                 | Min        | Max        |       |  |  |  |  |

| Α                      | 0.585      | 0.605      | 0.625 |  |  |  |  |

| A1                     | 0.175      | 0.200      | 0.225 |  |  |  |  |

| A2                     | 0.385      | 0.405      | 0.425 |  |  |  |  |

| D                      | 1.935      | 1.965      | 1.995 |  |  |  |  |

| D1                     | 1.600 BSC  |            |       |  |  |  |  |

| E                      | 1.410      | 1.440      | 1.470 |  |  |  |  |

| E1                     |            | 0.800 BSC  |       |  |  |  |  |

| b                      | 0.235      | 0.260      | 0.285 |  |  |  |  |

| е                      |            | 0.400 BSC  |       |  |  |  |  |

| x1                     | 0.320 REF  |            |       |  |  |  |  |

| x2                     | 0.320 REF  |            |       |  |  |  |  |

| y1                     | 0.1825 REF |            |       |  |  |  |  |

| y2                     |            | 0.1825 REF |       |  |  |  |  |

|                        |            |            |       |  |  |  |  |

## **CONTACT US**

**D**ioo is a professional design and sales corporation for high-quality and performance analog semiconductors. The company focuses on industry markets, such as cell phones, handheld products, laptops, medical equipment, and so on. Dioo's product families include analog signal processing and amplifying, LED drivers, and charger ICs. Go to <a href="http://www.dioo.com">http://www.dioo.com</a> for a complete list of Dioo product families

For additional product information or full datasheet, please contact our sales department or representatives.