## DIO7961

# 450 mA, Ultra-Low Noise and High PSRR LDO for Radio Frequency and Analog Circuits

## Features

- Operating input voltage range: 1.65 V to 5.5 V

- Available in fixed voltage option: 1 V to 3.3 V

- Output current: 450 mA

- Ultra high PSRR: Typ. 95 dB at  $f = 1$  kHz

- Ultra low noise: 10  $\mu$ V<sub>RMS</sub>

- Output voltage accuracy:  $\pm 1\%$

- Ultra-low quiescent current : Typ. 18  $\mu$ A

- Standby current: Typ. 0.1  $\mu$ A

- Very low dropout: 180 mV at 450 mA

- Stable with a 1  $\mu$ F small case size ceramic capacitor

- Quick output discharge:

DIO7961A: available

DIO7961B: not available

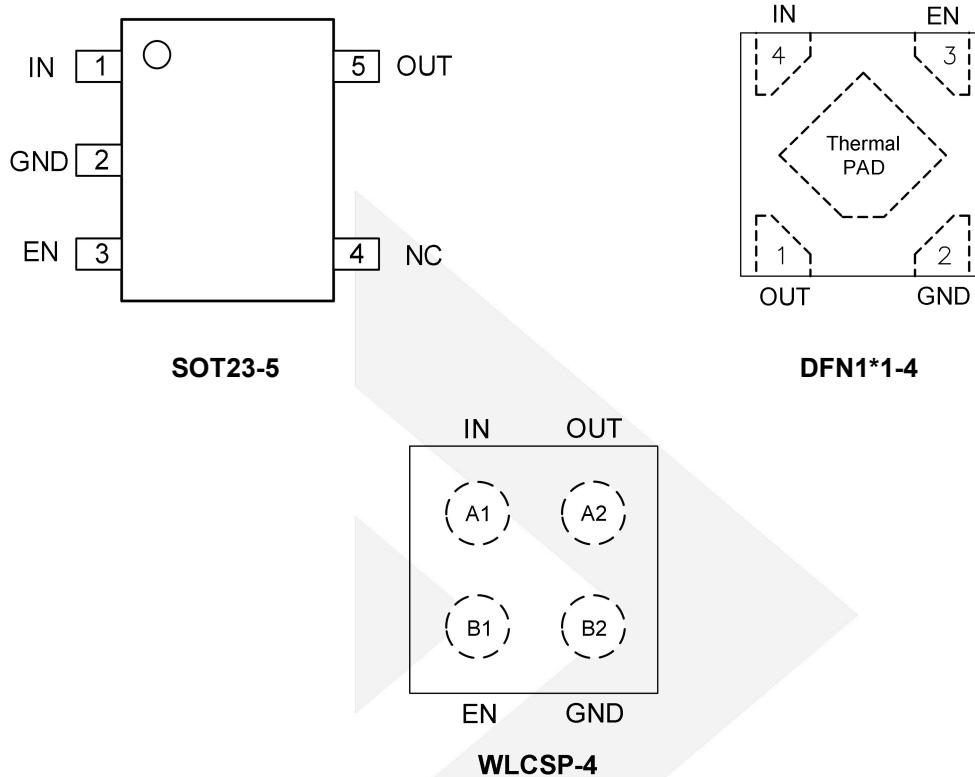

- Small package: SOT23-5, DFN1\*1-4 and WLCSP-4 (0.65 mm\*0.65 mm\*0.33 mm, pitch 0.35 mm) packages

## Descriptions

The DIO7961 series is a 450 mA, ultra-high PSRR, ultra-low noise, high-accuracy, and low dropout CMOS linear regulator with high ripple rejection. The device is ideal for radio frequency and analog circuits for its low quiescent current consumption and fast line and load transient performance. The DIO7961 operates over an input voltage range of 1.65 V to 5.5 V and supports fixed output voltage from 1 V to 3.3 V.

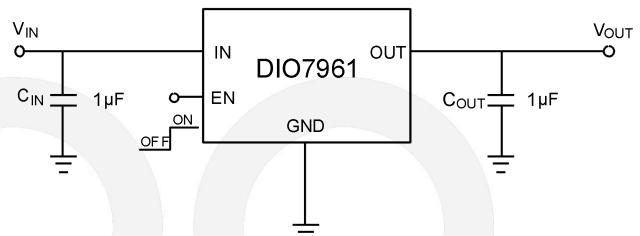

The DIO7961 is designed to work with a 1  $\mu$ F input and a 1  $\mu$ F output ceramic capacitor, allowing for a small overall solution size. A precision band-gap and error amplifier provide high accuracy of  $\pm 1\%$  (max) at 25°C. It is available in SOT23-5, WLCSP-4 (0.65 mm\*0.65 mm\*0.33 mm, pitch 0.35 mm) and DFN1\*1-4 packages.

## Applications

- Smartphones

- Tablets

- IP cameras

- RF, PLL, VCO and clock power supply

- Portable medical equipment

## Typical Application

Figure 1. Typical Application

DIO7961

## Ordering Information

| Order Part Number | Top Marking | Description          |       | T <sub>A</sub> | Package  |                    |

|-------------------|-------------|----------------------|-------|----------------|----------|--------------------|

| DIO7961AaaWL4     | W3X         | Active Discharge     | Green | -40 to +125°C  | WLCSP-4  | Tape & Reel, 5000  |

| DIO7961AaaEN4     | YW3X        |                      | Green | -40 to +125°C  | DFN1*1-4 | Tape & Reel, 10000 |

| DIO7961AaaST5     | A3XYW       |                      | Green | -40 to +125°C  | SOT23-5  | Tape & Reel, 3000  |

| DIO7961BaaWL4     | W4X         | Non-Active Discharge | Green | -40 to +125°C  | WLCSP-4  | Tape & Reel, 5000  |

| DIO7961BaaEN4     | YW4X        |                      | Green | -40 to +125°C  | DFN1*1-4 | Tape & Reel, 10000 |

| DIO7961BaaST5     | A4XYW       |                      | Green | -40 to +125°C  | SOT23-5  | Tape & Reel, 3000  |

### Output Voltage Options

| Option Code "aa" | 10    | 12    | 15    | 18    | 25    | 28    | 30  | 33    |

|------------------|-------|-------|-------|-------|-------|-------|-----|-------|

| Voltage          | 1.0 V | 1.2 V | 1.5 V | 1.8 V | 2.5 V | 2.8 V | 3 V | 3.3 V |

### Marking Definition

|       |                                               |

|-------|-----------------------------------------------|

| W3X   | W: Week code; 3: Product code;                |

| YW3X  | Y: Year code; W: Week code; 3: Product code;  |

| A3XYW | A3: Product code; Y: year code; W: week code; |

| W4X   | W: Week code; 4: Product code;                |

| YW4X  | Y: Year code; W: week code; 4: Product code;  |

| A4XYW | A4: Product code; Y: year code; W: Week code; |

### Voltage code

| Option Code "X" | E     | F     | G     | H     | J     | K     | L   | M     |

|-----------------|-------|-------|-------|-------|-------|-------|-----|-------|

| Voltage         | 1.0 V | 1.2 V | 1.5 V | 1.8 V | 2.5 V | 2.8 V | 3 V | 3.3 V |

450 mA, Ultra-Low Noise and High PSRR LDO for RF and Analog Circuits

## Pin Assignments

**Figure 2. Pin Assignment (Top View)**

## Pin Definitions

| Pin Name    | Description                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT         | Regulated output voltage. The output should be bypassed with a small 1 $\mu$ F ceramic capacitor.                                                                     |

| EN          | Enable Pin. This pin has an internal pull-down resistor. A logic low reduces the supply current to less than 1 $\mu$ A. Connect to logic "High" for normal operation. |

| GND         | Power Supply Ground                                                                                                                                                   |

| IN          | Input voltage supply pin                                                                                                                                              |

| Thermal PAD | No connection                                                                                                                                                         |

## Absolute Maximum Ratings

Stresses beyond those listed under the Absolute Maximum Rating table may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol       | Parameter                           | Rating                        | Unit  |

|--------------|-------------------------------------|-------------------------------|-------|

| $V_{IN}$     | Input voltage                       | -0.3 V to 6                   | V     |

| $V_{OUT}$    | Output voltage                      | -0.3 to $V_{IN}$ + 0.3, max.6 | V     |

| $V_{CE}$     | Chip enable input                   | -0.3 to 6                     | V     |

| $t_{sc}$     | Output short circuit duration       | unlimited                     | s     |

| $T_{J(MAX)}$ | Maximum junction temperature        | 150                           | °C    |

| $T_{STG}$    | Storage temperature                 | -55 to 150                    | °C    |

| $R_{θJA}$    | Thermal resistance, junction-to-air | WLCSP-4                       | 108   |

|              |                                     | DFN1*1-4                      | 198.1 |

|              |                                     | SOT23-5                       | 218   |

| ESD          | Human body model (HBM)              | 4000                          | V     |

|              | Charged device model (CDM)          | 2000                          |       |

## Recommend Operating Conditions

Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. DIOO does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol   | Parameter                      | Rating      | Unit |

|----------|--------------------------------|-------------|------|

| $V_{IN}$ | Input voltage                  | 1.65 to 5.5 | V    |

| $T_A$    | Operating free-air temperature | -40 to 125  | °C   |

## Electrical Characteristics

$-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ ;  $V_{IN} = V_{OUT(NOM)} + 1\text{ V}$ ;  $I_{OUT} = 1\text{ mA}$ ,  $C_{IN} = C_{OUT} = 1\text{ }\mu\text{F}$ , unless otherwise noted.  $V_{EN} = 1.0\text{ V}$ . Typical values are at  $T_J = 25^\circ\text{C}$ .

| Symbol                     | Parameter               | Test Conditions                                                                   |                               | Min  | Typ  | Max | Unit          |

|----------------------------|-------------------------|-----------------------------------------------------------------------------------|-------------------------------|------|------|-----|---------------|

| $V_{IN}$                   | Operating input voltage |                                                                                   |                               | 1.65 |      | 5.5 | V             |

| $V_{OUT}$                  | Output voltage accuracy | $V_{IN} = V_{OUT(NOM)} + 1\text{ V}$                                              | $V_{OUT} < 2\text{ V}$        | -20  |      | +20 | mV            |

|                            |                         | $I_{OUT} = 1\text{ mA}$ , $T_J = 25^\circ\text{C}$                                | $V_{OUT} \geq 2\text{ V}$     | -1   |      | +1  | %             |

| $\text{Line}_{\text{Reg}}$ | Line regulation         | $V_{OUT(NOM)} + 1\text{ V} < V_{IN} \leq 5.5\text{ V}$ , $T_J = 25^\circ\text{C}$ |                               |      |      | 6   | mV            |

| $\text{Load}_{\text{Reg}}$ | Load regulation         | $I_{OUT} = 1\text{ mA to } 450\text{ mA}$ ,<br>$T_J = 25^\circ\text{C}$           | WLCSP-4                       |      | 2    |     | mV            |

|                            |                         |                                                                                   | DFN1*1-4                      |      |      | 30  |               |

|                            |                         |                                                                                   | SOT23-5                       |      |      | 36  |               |

| $V_{DO}$                   | Dropout voltage         | $I_{OUT} = 450\text{ mA}$ ,<br>$T_A = 25^\circ\text{C}$ ,<br>WLCSP-4              | $V_{OUT(NOM)} = 1.8\text{ V}$ |      | 235  | 300 | mV            |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.0\text{ V}$ |      | 180  | 250 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.5\text{ V}$ |      | 150  | 190 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.8\text{ V}$ |      | 135  | 175 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 3.0\text{ V}$ |      | 120  | 150 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 3.3\text{ V}$ |      | 110  | 145 |               |

| $V_{DO}$                   | Dropout voltage         | $I_{OUT} = 450\text{ mA}$ ,<br>$T_A = 25^\circ\text{C}$ ,<br>DFN1*1-4             | $V_{OUT(NOM)} = 1.8\text{ V}$ |      | 270  | 335 | mV            |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.0\text{ V}$ |      | 215  | 285 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.5\text{ V}$ |      | 185  | 225 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.8\text{ V}$ |      | 170  | 210 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 3.0\text{ V}$ |      | 155  | 190 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 3.3\text{ V}$ |      | 145  | 180 |               |

| $V_{DO}$                   | Dropout voltage         | $I_{OUT} = 450\text{ mA}$ ,<br>$T_A = 25^\circ\text{C}$ ,<br>SOT23-5              | $V_{OUT(NOM)} = 1.8\text{ V}$ |      | 300  | 370 | mV            |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.0\text{ V}$ |      | 250  | 320 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.5\text{ V}$ |      | 210  | 260 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 2.8\text{ V}$ |      | 200  | 250 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 3.0\text{ V}$ |      | 180  | 225 |               |

|                            |                         |                                                                                   | $V_{OUT(NOM)} = 3.3\text{ V}$ |      | 170  | 215 |               |

| $I_{CL}$                   | Output current limit    | $V_{OUT} = 90\% V_{OUT(NOM)}$                                                     |                               | 450  | 700  |     | mA            |

| $I_{SC}$                   | Short circuit current   | $V_{OUT} = 0\text{ V}$                                                            |                               |      | 180  |     | mA            |

| $I_Q$                      | Quiescent current       | $I_{OUT} = 0\text{ mA}$ , $T_J = 25^\circ\text{C}$                                |                               |      | 18   | 25  | $\mu\text{A}$ |

| $I_{DIS}$                  | Shutdown current        | $V_{EN} \leq 0.4\text{ V}$ , $V_{IN} = 4.8\text{ V}$ , $T_J = 25^\circ\text{C}$   |                               |      | 0.01 | 1   | $\mu\text{A}$ |

| $V_{ENH}$                  | EN pin threshold        | EN input voltage "H"                                                              |                               | 1    |      |     | V             |

**450 mA, Ultra-Low Noise and High PSRR LDO for RF and Analog Circuits**

|                      |                                    |                                                                                                                                      |                            |     |     |     |                            |

|----------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|-----|-----|----------------------------|

| $V_{EN}$             | voltage                            | EN input voltage "L"                                                                                                                 |                            |     |     | 0.4 | V                          |

| $I_{EN}$             | EN pull down current               | $V_{EN} = 4.8 \text{ V}$ , $T_J = 25^\circ\text{C}$                                                                                  |                            |     | 0.1 | 0.5 | $\mu\text{A}$              |

| $t_{ON}$             | Turn on time                       | $V_{OUT} = 1 \mu\text{F}$ , from assertion of $V_{EN}$ to $V_{OUT} = 95\% V_{OUT(NOM)}$                                              |                            |     | 250 |     | $\mu\text{s}$              |

| PSRR                 | Power supply rejection ratio       | $I_{OUT} = 10 \text{ mA}$                                                                                                            | $f = 100 \text{ Hz}$       |     | 91  |     | dB                         |

|                      |                                    |                                                                                                                                      | $f = 1 \text{ kHz}$        |     | 95  |     |                            |

|                      |                                    |                                                                                                                                      | $f = 10 \text{ kHz}$       |     | 75  |     |                            |

|                      |                                    |                                                                                                                                      | $f = 100 \text{ kHz}$      |     | 55  |     |                            |

|                      |                                    |                                                                                                                                      | $f = 1 \text{ MHz}$        |     | 56  |     |                            |

| $V_N$                | Output voltage noise               | $f = 10 \text{ Hz to } 100 \text{ kHz}$                                                                                              | $I_{OUT} = 1 \text{ mA}$   |     | 14  |     | $\mu\text{V}_{\text{RMS}}$ |

|                      |                                    |                                                                                                                                      | $I_{OUT} = 450 \text{ mA}$ |     | 10  |     |                            |

| $R_{DIS}$            | Active output discharge resistance | $V_{EN} < 0.4 \text{ V}$ , version A only                                                                                            |                            |     | 100 |     | $\Omega$                   |

| Tran <sub>LINE</sub> | Line transient                     | $V_{IN} = (V_{OUT(NOM)} + 1 \text{ V}) \text{ to } (V_{OUT(NOM)} + 1.6 \text{ V})$<br>in 30 $\mu\text{s}$ , $I_{OUT} = 1 \text{ mA}$ |                            | -1  |     | mV  |                            |

|                      |                                    | $V_{IN} = (V_{OUT(NOM)} + 1.6 \text{ V}) \text{ to } (V_{OUT(NOM)} + 1 \text{ V})$<br>in 30 $\mu\text{s}$ , $I_{OUT} = 1 \text{ mA}$ |                            |     |     |     |                            |

| Tran <sub>LOAD</sub> | Load transient                     | $I_{OUT} = 1 \text{ mA to } 450 \text{ mA in } 10 \mu\text{s}$                                                                       |                            | -40 |     | mV  |                            |

|                      |                                    | $I_{OUT} = 450 \text{ mA to } 1 \text{ mA in } 10 \mu\text{s}$                                                                       |                            |     |     |     |                            |

| $T_{SDH}$            | Thermal shutdown threshold         | Temperature rising                                                                                                                   |                            |     | 160 |     | $^\circ\text{C}$           |

| $T_{SDL}$            |                                    | Temperature falling                                                                                                                  |                            |     | 140 |     | $^\circ\text{C}$           |

Note: Specifications subject to change without notice.

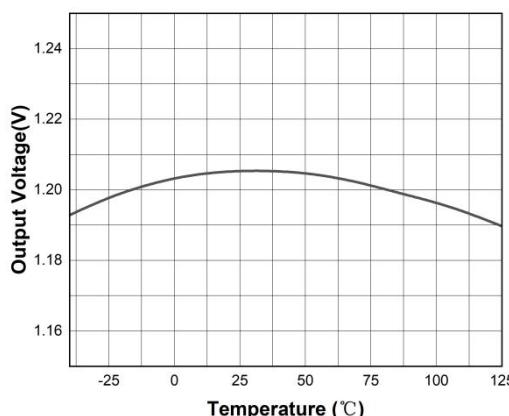

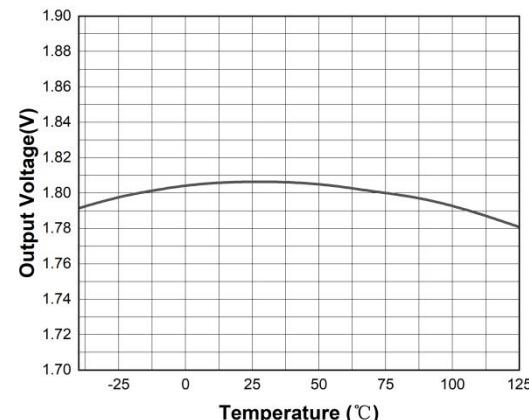

## Typical Performance Characteristics

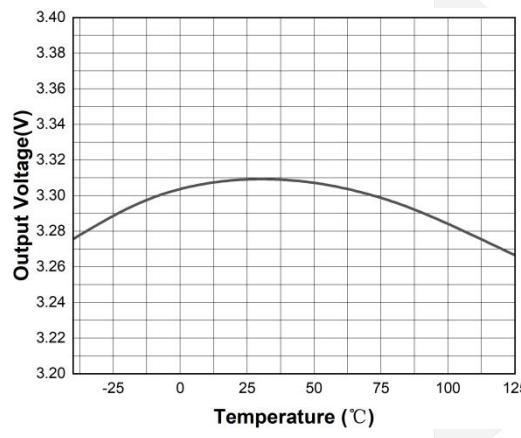

$V_{OUT} = 1.2 \text{ V}$ ,  $C_{IN} = C_{OUT} = 1 \mu\text{F}$ ,  $I_{OUT} = 1 \text{ mA}$

**Figure 3. Output Voltage vs Temperature**

$V_{OUT} = 1.8 \text{ V}$ ,  $C_{IN} = C_{OUT} = 1 \mu\text{F}$ ,  $I_{OUT} = 1 \text{ mA}$

**Figure 4. Output Voltage vs Temperature**

$V_{OUT} = 3.3 \text{ V}$ ,  $C_{IN} = C_{OUT} = 1 \mu\text{F}$ ,  $I_{OUT} = 1 \text{ mA}$

**Figure 5. Output Voltage vs Temperature**

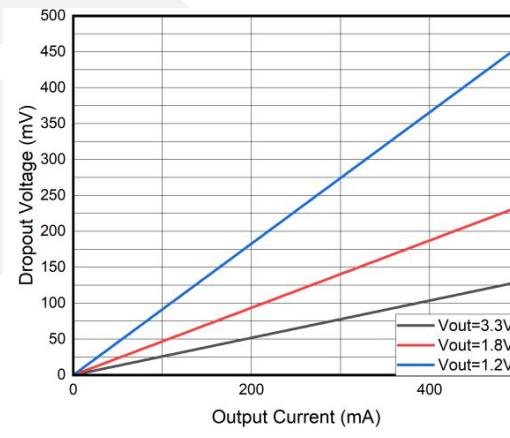

**Figure 6. Dropout Voltage vs Output Current**

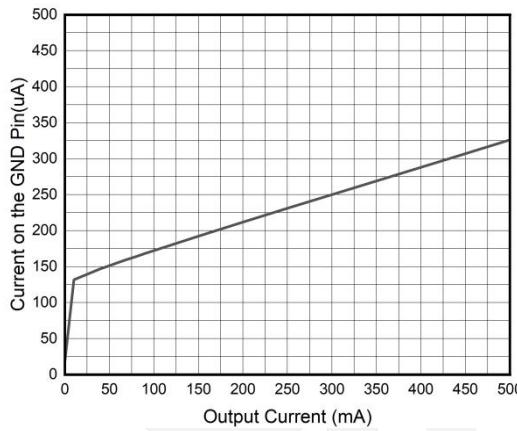

$C_{OUT} = 1 \mu\text{F}$ ,  $V_{IN} = 2.2 \text{ V}$ ,  $V_{OUT} = 1.2 \text{ V}$

**Figure 7. Current on the GND Pin vs Output Current**

**450 mA, Ultra-Low Noise and High PSRR LDO for RF and Analog Circuits**

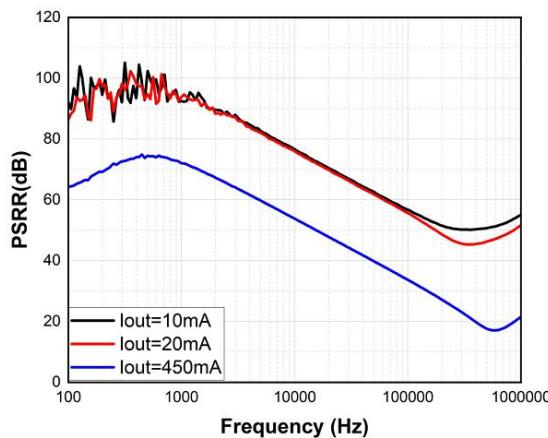

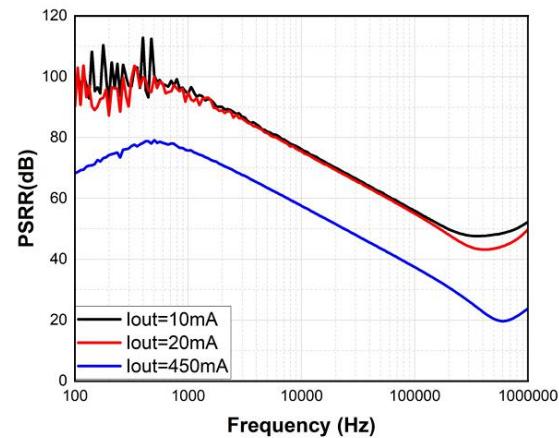

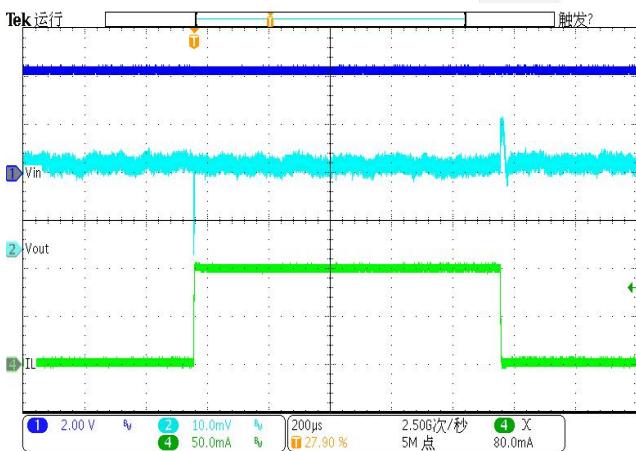

$V_{IN} = 2.8 \text{ V} + 200 \text{ mVPP}, V_{OUT} = 1.8 \text{ V}, C_{OUT} = 1 \text{ uF}$

**Figure 8. PSRR vs Frequency**

$V_{IN} = 4.3 \text{ V} + 200 \text{ mVPP}, V_{OUT} = 3.3 \text{ V}, C_{OUT} = 1 \text{ uF}$

**Figure 9. PSRR vs Frequency**

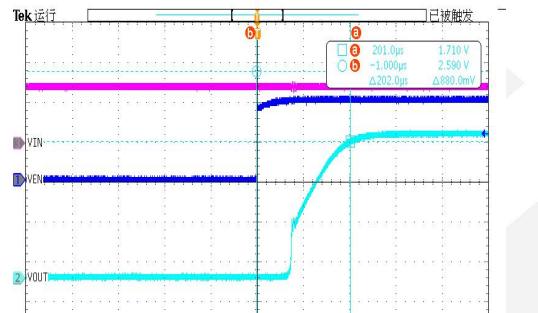

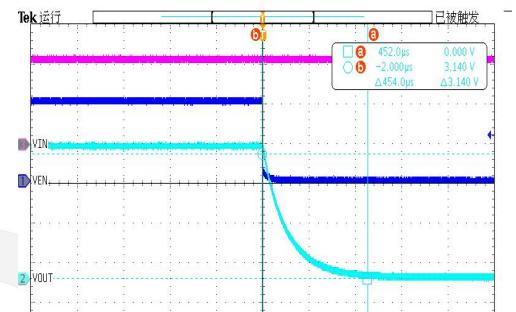

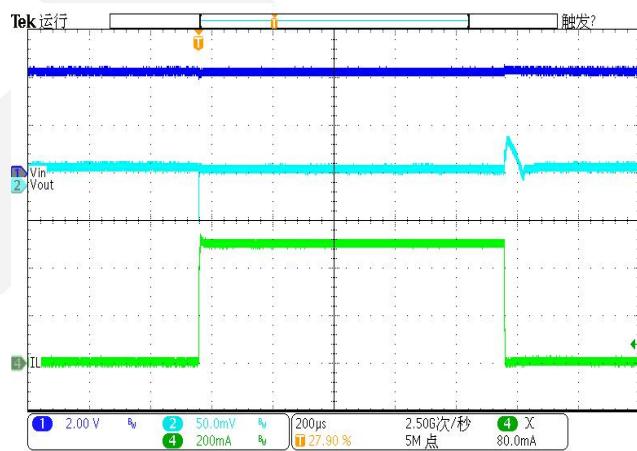

$V_{IN} = 2.8 \text{ V}, V_{OUT} = 1.8 \text{ V}, C_{IN} = C_{OUT} = 1 \text{ uF}, IL = 1 \text{ mA}$

From assertion of  $V_{EN}$  to  $V_{OUT} = 95\% V_{OUT(NOM)}$

**Figure 10. Turn On Time**

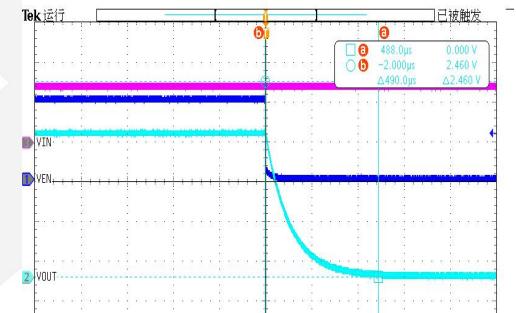

$V_{IN} = 2.8 \text{ V}, V_{OUT} = 1.8 \text{ V}, C_{IN} = C_{OUT} = 1 \text{ uF}, IL = 1 \text{ mA}$

From assertion of  $V_{EN}$  to  $V_{OUT} = 0$

**Figure 11. Turn Off Time**

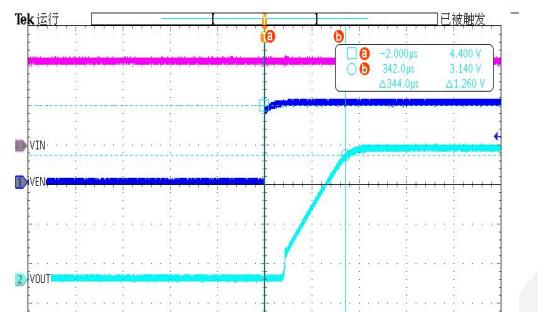

$V_{IN} = 4.3 \text{ V}, V_{OUT} = 3.3 \text{ V}, C_{IN} = C_{OUT} = 1 \text{ uF}, IL = 1 \text{ mA}$

From assertion of  $V_{EN}$  to  $V_{OUT} = 95\% V_{OUT(NOM)}$

**Figure 12. Turn On Time**

$V_{IN} = 4.3 \text{ V}, V_{OUT} = 3.3 \text{ V}, C_{IN} = C_{OUT} = 1 \text{ uF}, IL = 1 \text{ mA}$

From assertion of  $V_{EN}$  to  $V_{OUT} = 0$

**Figure 13. Turn Off Time**

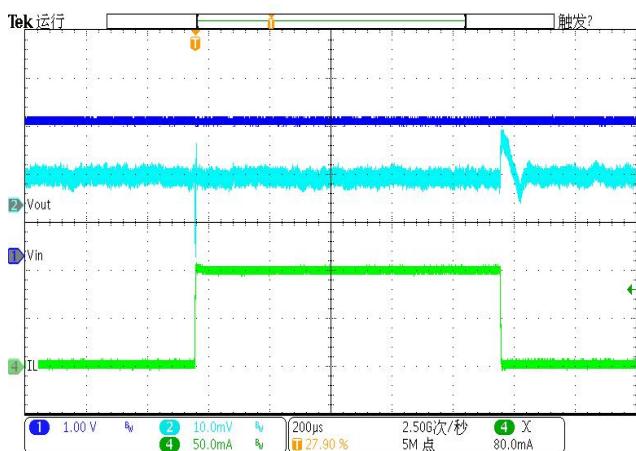

$V_{IN} = 2.8 \text{ V}$ ,  $V_{OUT} = 1.8 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$ ,  $I_{OUT} = 1 \text{ mA to } 100 \text{ mA}$

**Figure 14. Load Transient Response**

$V_{IN} = 2.8 \text{ V}$ ,  $V_{OUT} = 1.8 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$ ,  $I_{OUT} = 1 \text{ mA to } 500 \text{ mA}$

**Figure 15. Load Transient Response**

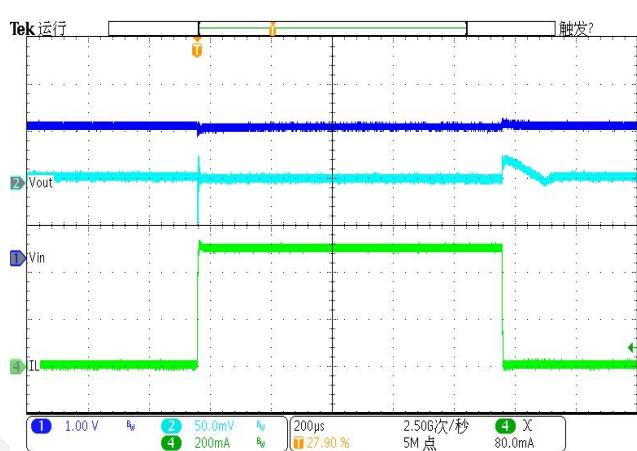

$V_{IN} = 4.3 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$ ,  $I_{OUT} = 1 \text{ mA to } 100 \text{ mA}$

**Figure 16. Load Transient Response**

$V_{IN} = 4.3 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $C_{OUT} = 1 \mu\text{F}$ ,  $I_{OUT} = 1 \text{ mA to } 500 \text{ mA}$

**Figure 17. Load Transient Response**

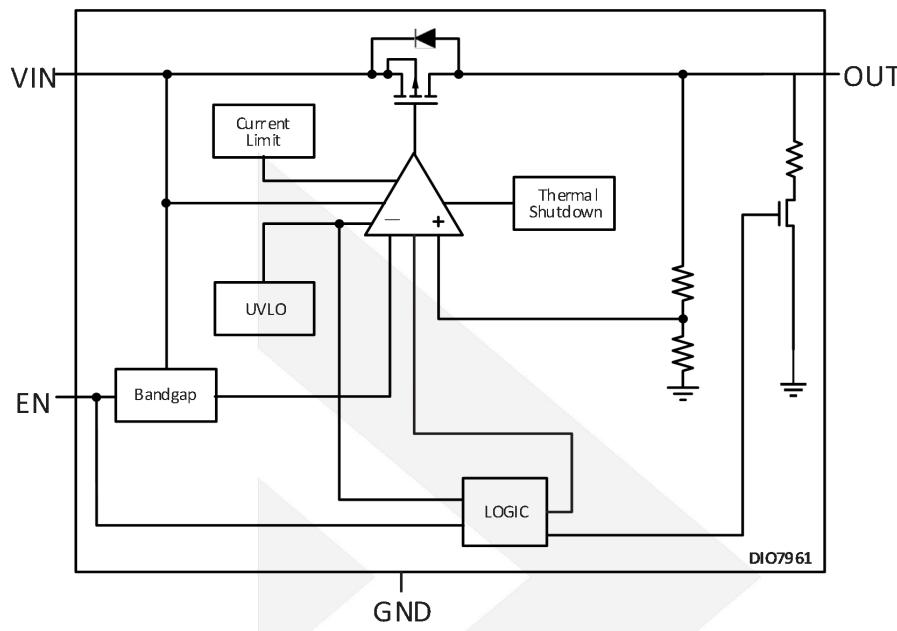

## Block Diagram

## Detailed Description

### Overview

The DIO7961 series of LDO linear regulators are ultra-high PSRR and low noise devices with excellent line and load transient performance. These LDOs are designed for power-sensitive applications. A precision bandgap and error amplifier provide overall 1% accuracy. Low output noise, very high PSRR, and low dropout voltage make this device ideal for most battery-operated handheld equipment. The DIO7961 is fully protected in case of current overload, output short circuit, and overheating.

### Input Capacitor Selection ( $C_{IN}$ )

The DIO7961 is specifically designed to work with a standard ceramic input capacitor. An input capacitor connected as close as possible is necessary to ensure device stability. The X7R or X5R capacitor should be used because of its minimal variation in values and equivalent series resistance (ESR) over temperature. The value of the input capacitor should be 1  $\mu$ F or larger to ensure the optimum dynamic performance. As far as unwanted AC signals or noise modulated onto constant input voltage are concerned, this capacitor will provide a low impedance path for them. Use ceramic capacitors for the best because they have low ESR and ESL. The input capacitor has no ESR restrictions as long as it can limit the influence of input trace inductance and source resistance during sudden load current changes.

### Output Capacitor Selection ( $C_{OUT}$ )

The DIO7961 requires an output capacitance. The value of the input capacitor should be 1  $\mu$ F or larger for stability. Use X5R-type or X7R-type ceramic capacitor because of its minimal variation in values and ESR over temperature.

An output capacitor with a maximum value of ESR less than  $2\ \Omega$  is for the best though there are no requirements for the minimum ESR of the capacitor. With larger output capacitors and lower ESR, one can expect better load transient response or high-frequency PSRR, which is why tantalum capacitors on the output is a good option. Low temperatures increase the equivalent series resistance of tantalum capacitors.

### Enable Operation

The DIO7961 uses the EN pin to enable or disable its device and discharge function (just for DIO7961A). If the EN pin voltage is pulled below 0.4 V, the device is guaranteed to be disabled. The active discharge transistor in the devices with the active discharge feature is activated and the output voltage  $V_{OUT}$  is pulled to GND through an internal circuitry with an effective resistance of about 100 ohms.

If the EN pin voltage is higher than 1.0 V the device is guaranteed to be enabled. The internal active discharge circuitry is switched off and the desired output voltage is available at the output pin. The EN pin should be connected directly to the input pin when there is no need for the EN function.

### Output Current Limit

The DIO7961 internal current limit helps to protect the regulator during fault conditions. Output Current is internally limited within the IC to a typical 700 mA. During the current limit, the output sources a fixed amount of current that is largely independent of the output voltage. In such a case, the output voltage is not regulated, and  $V_{OUT} = I_{CL} \times R_{LOAD}$ . The PMOS pass transistor dissipates  $(V_{IN} - V_{OUT}) \times I_{CL}$  until the thermal shutdown is triggered and the device turns off. As the device cools down, it is turned on by the internal thermal shutdown circuit. If the fault condition continues, the device cycles between the current limit and thermal shutdown.

The PMOS pass element in the DIO7961 has a built-in body diode that conducts current when the voltage at OUT exceeds the voltage at IN. This current is not limited, so if extended reverse voltage operation is anticipated, external limiting to 5% of the rated output current is recommended.

### Thermal Shutdown

When the chip temperature exceeds the Thermal Shutdown point ( $T_{SD} = 160^{\circ}\text{C}$  typical), the device goes to the disabled state and the output voltage is not delivered until the die temperature decrease to  $140^{\circ}\text{C}$ . The Thermal Shutdown feature protects from a catastrophic device failure at accidental overheating. Using this protection in place of proper heat sinking is not recommended.

### Dropout Voltage

The DIO7961 uses a PMOS pass transistor to achieve low dropout. When  $(V_{IN} - V_{OUT})$  is less than the dropout voltage ( $V_{DO}$ ), the PMOS pass device is in the linear region of operation and the input-to-output resistance is the  $R_{DS(on)}$  of the PMOS pass element.  $V_{DO}$  scales approximately with output current because the PMOS device behaves as a resistor in dropout.

### Power Dissipation and Heat Sinking

The design and layout of the board determine how much power can be dissipated by the device. A part's junction temperature rise is affected by how the mounting pads are configured on the PCB, the material of the PCB, and the ambient temperature. The maximum power dissipation the DIO7961 device can handle is given by:

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_A}{R_{\theta JA}}$$

The power dissipated by the DIO7961 device for given application conditions can be calculated from the following equations:

$$P_D \approx V_{IN} \cdot I_{GND} + I_{OUT}(V_{IN} - V_{OUT})$$

### Reverse Current

Reverse current flows through the body diode on the pass element instead of the normal conducting channel in the case that  $V_{OUT} > V_{IN}$ . Excessive reverse current can damage this device, which is why the device may require additional external protection when there could be an extended reverse current condition.

### Power Supply Rejection Ratio

The DIO7961 features a very high Power Supply Rejection ratio to meet the requirements of RF and analog circuits. By the selection of the  $C_{OUT}$  capacitor and proper PCB layout, the PSRR at higher frequencies in the range 100 kHz – 10 MHz can be tuned.

### Turn-On Time

The turn-on time is defined as the time period from EN activation to the point in which  $V_{OUT}$  will reach 98% of its nominal value. The time is dependent on various application conditions such as  $V_{OUT(NOM)}$ ,  $C_{OUT}$ ,  $T_A$ .

### PCB Layout Recommendations

An optimal layout can greatly improve transient performance, PSRR, and noise.  $C_{IN}$  and  $C_{OUT}$  capacitors should be placed near device pins and PCB traces should be widely spaced for excellent performance. Place ground return connections to the input and output capacitors. Larger copper area connected to the pins will also improve the device thermal resistance. For better power dissipation and lower device temperatures, tie the exposed pad to the GND pin.

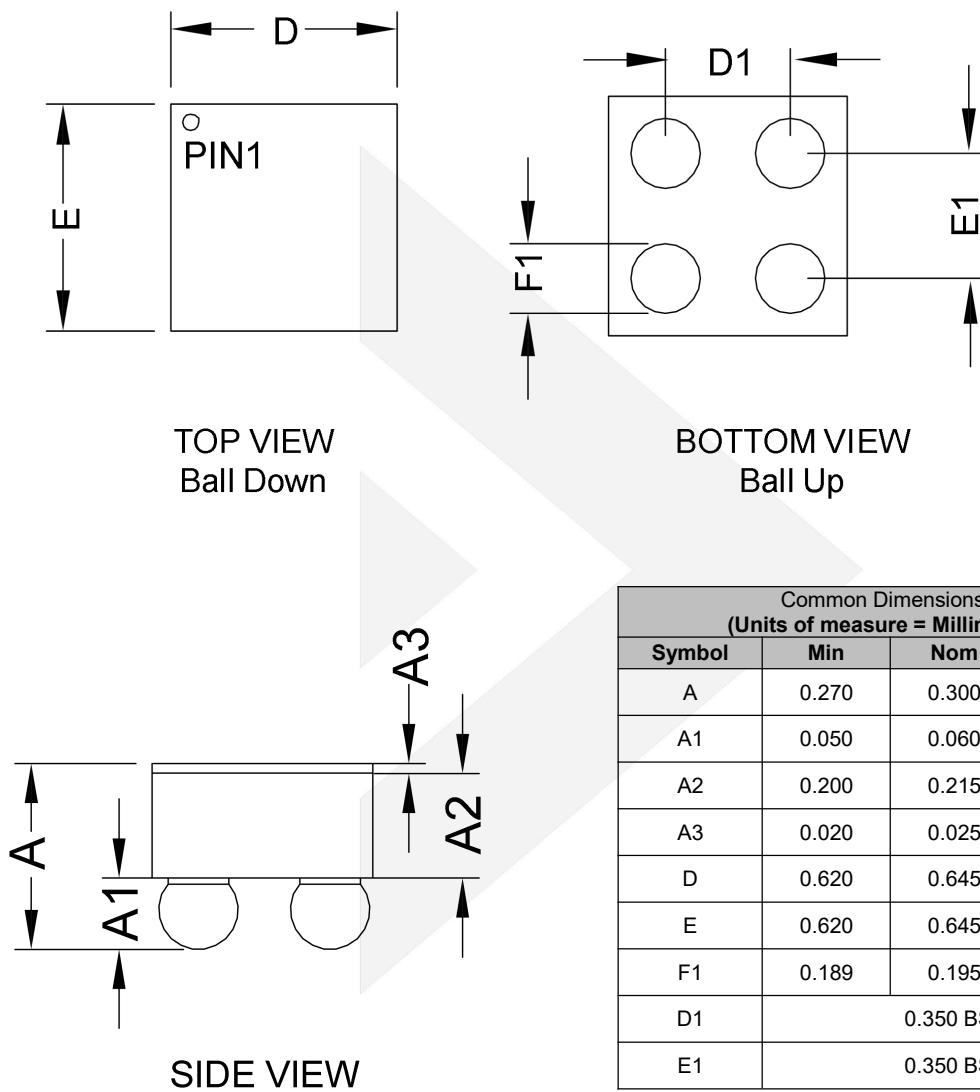

## Physical Dimensions: WLCSP-4

450 mA, Ultra-Low Noise and High PSRR LDO for RF and Analog Circuits

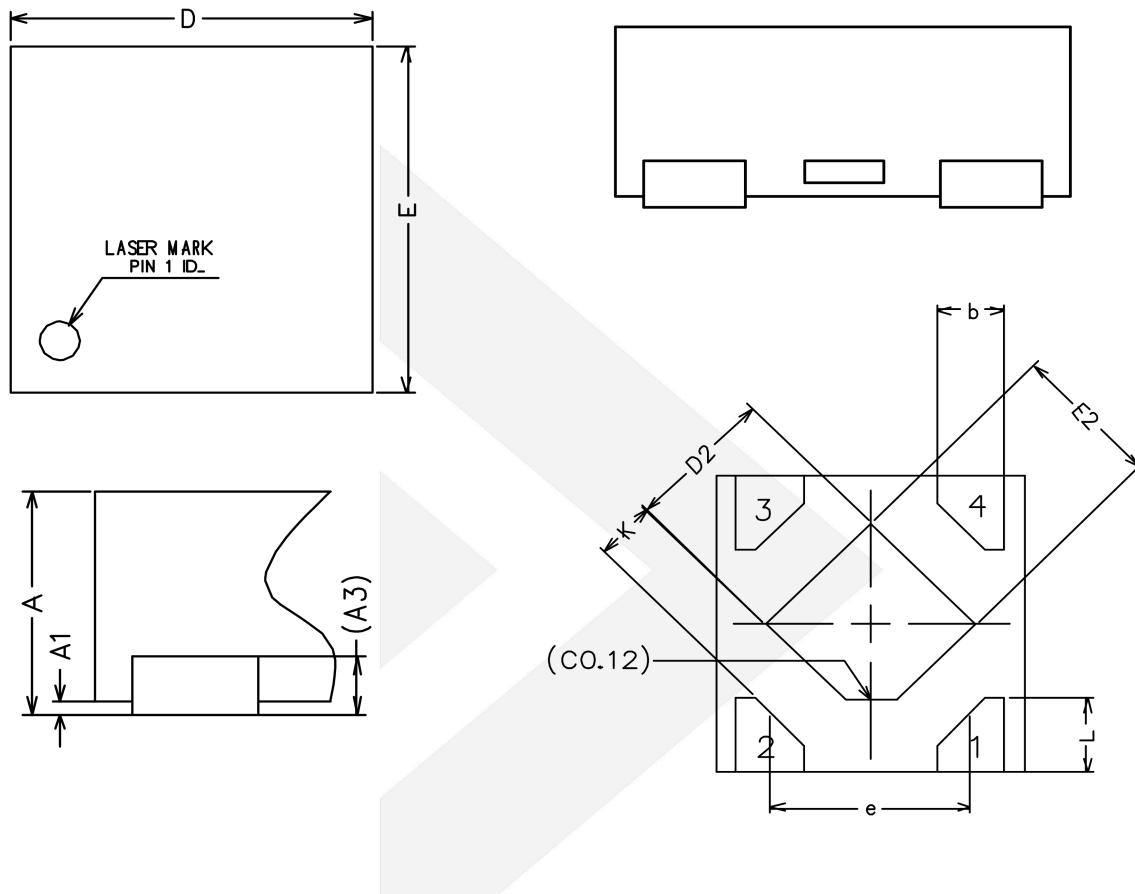

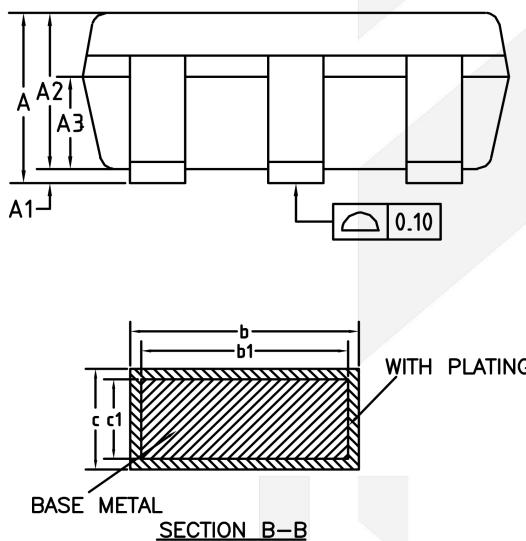

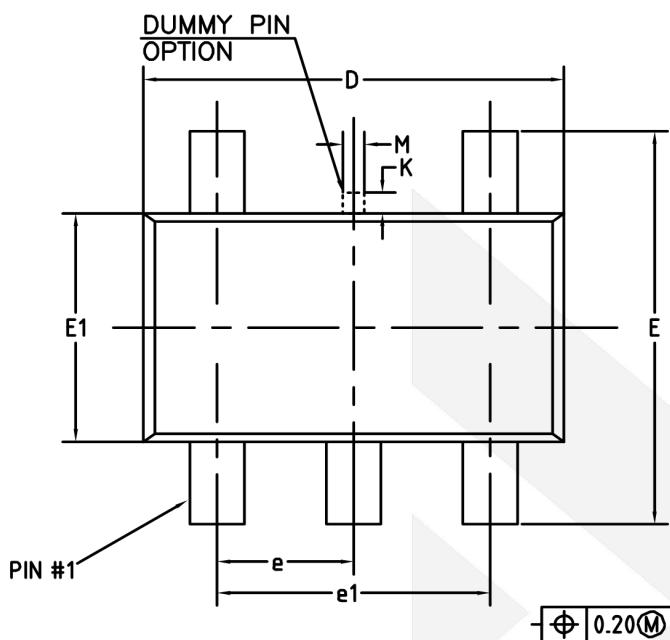

## Physical Dimensions: DFN1\*1-4

| Common Dimensions<br>(Units of measure = Millimeter) |            |      |      |

|------------------------------------------------------|------------|------|------|

| Symbol                                               | Min        | Nom  | Max  |

| A                                                    | 0.34       | 0.37 | 0.40 |

| A1                                                   | 0.00       | 0.02 | 0.05 |

| A3                                                   | 0.100 REF. |      |      |

| b                                                    | 0.17       | 0.22 | 0.27 |

| D                                                    | 0.95       | 1.00 | 1.05 |

| E                                                    | 0.95       | 1.00 | 1.05 |

| D2                                                   | 0.43       | 0.48 | 0.53 |

| E2                                                   | 0.43       | 0.48 | 0.53 |

| L                                                    | 0.20       | 0.25 | 0.30 |

| e                                                    | 0.65 BSC.  |      |      |

| K                                                    | 0.15       | -    | -    |

**450 mA, Ultra-Low Noise and High PSRR LDO for RF and Analog Circuits**

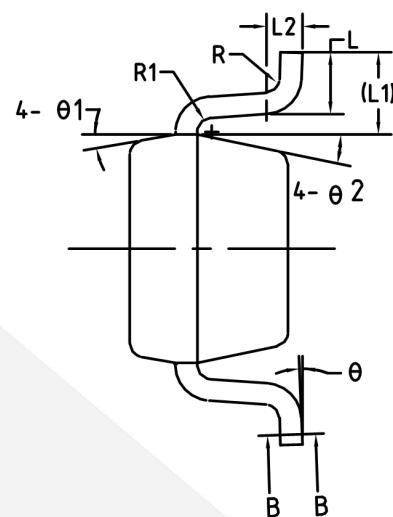

## Physical Dimensions: SOT23-5

| Symbol | Dimensions in Millimeters |          |       |

|--------|---------------------------|----------|-------|

|        | Min                       | Nom      | Max   |

| A      | -                         | -        | 1.25  |

| A1     | 0                         | -        | 0.15  |

| A2     | 1.00                      | 1.10     | 1.20  |

| A3     | 0.60                      | 0.65     | 0.70  |

| b      | 0.36                      | -        | 0.45  |

| b1     | 0.35                      | 0.38     | 0.41  |

| c      | 0.14                      | -        | 0.20  |

| c1     | 0.14                      | 0.15     | 0.16  |

| D      | 2.826                     | 2.926    | 3.026 |

| E      | 2.60                      | 2.80     | 3.00  |

| E1     | 1.526                     | 1.626    | 1.726 |

| e      | 0.90                      | 0.95     | 1.00  |

| e1     | 1.80                      | 1.90     | 2.00  |

| K      | 0                         | -        | 0.25  |

| L      | 0.30                      | 0.40     | 0.60  |

| L1     |                           | 0.59 REF |       |

| L2     |                           | 0.25 BSC |       |

| M      | 0.10                      | 0.15     | 0.25  |

| R      | 0.05                      | -        | 0.20  |

| R1     | 0.05                      | -        | 0.20  |

| θ      | 0°                        | -        | 8°    |

| θ1     | 8°                        | 10°      | 12°   |

| θ2     | 10°                       | 12°      | 14°   |

## CONTACT US

Dioo is a professional design and sales corporation for high-quality and performance analog semiconductors. The company focuses on industry markets, such as cell phones, handheld products, laptops, medical equipment, and so on. Dioo's product families include analog signal processing and amplifying, LED drivers, and charger ICs. Go to <http://www.dioo.com> for a complete list of Dioo product families.

For additional product information or full datasheet, please contact our sales department or representatives.