## DIO6833A

# High Efficiency, 2A, Two-Cell Boost Li-Ion Battery Charger Preliminary Specification

## Features

- Low profile QFN3x3 package for portable applications

- Integrated synchronous boost with 18V rating low  $R_{DS(ON)}$  FETs for high charge efficiency

- Charge voltage accuracy:  $\pm 0.5\%$

- Trickle current / Constant current / Constant voltage charge mode

- Adaptive input current limit with selectable threshold

- Maximum 2A constant charge current

- Charge current information indication

- Programmable charge timeout

- Programmable constant charge current

- Constant voltage selectable

- Thermal regulation protection

- External shutdown function

- Input voltage UVLO and OVP

- Over temperature protection

- Output short circuit protection

- Charge status indication

- Normal synchronous boost operation when battery removed

## Descriptions

The DIO6833A is a 4.375-5.5 V, 2 A two-cell synchronous boost Li-Ion battery charger integrates 1MHz switching frequency and full protection functions. The charge current up to 2A can be programmed by using the external resistor for different portable applications. The external resistor indicates the charger current information simultaneously. It also has a programmable charge timeout and adaptive input current limit with selectable threshold for safety battery charge operation. The DIO6833A can disconnect output when there is output short circuit or shutdown happens. It consists of 18V rating FETs with extremely low on resistance to achieve high charge efficiency and simple peripheral circuit design.

The DIO6833A along with small QFN3x3 footprint provides small PCB area application.

## Applications

- Cellular Telephones, PDA, MP3 Players, MP4 Players

- Digital Cameras

- Bluetooth Applications

- PSP Game Players, NDS Game Players

- Notebook

## Ordering Information

| Order Part Number | Top Marking |       | $T_A$       | Package   |                   |

|-------------------|-------------|-------|-------------|-----------|-------------------|

| DIO6833ACL16      | 6832A       | Green | -40 to 85°C | QFN3*3-16 | Tape & Reel, 5000 |

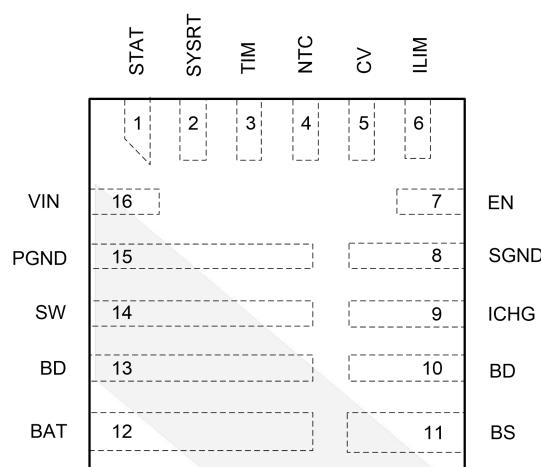

## Pin Assignments

**Figure 1 Pin Assignment (Top View)**

## Pin Definitions

| Pin name | Description                                                                                                                                                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW       | Switch node pin. Connect to external inductor.                                                                                                                                                                                                                                                                |

| STAT     | Charge status indication pin. It is open drain output pin and pull high to VIN thru a LED to indicate the charge in process. When the charge is off done, LED is off.                                                                                                                                         |

| VIN      | Analog power input pin. Connect a MLCC from this pin to ground to decouple high harmonic noise. This pin has OVP and UVLO function to make the charger operate within safe input voltage area.                                                                                                                |

| CV       | Battery CV voltage selection pin. Pull down for 8.4V cell voltage and pull up for 8.7V cell voltage.                                                                                                                                                                                                          |

| ILIM     | Input current limit setting Pin. Select the permitted minimum input voltage to trigger the input current limit function. Pull high for 4.5V, pull low for 4.375V, floating for 4.74V.                                                                                                                         |

| TIM      | Charge time limit pin. Connect this pin with a capacitor to ground. Internal current source charge the capacitor for charge time limit. TC charge time limit is about 1/10 of CC charge time.                                                                                                                 |

| ICHG     | Charge current program pin, pull down to GND with a resistor $R_{ICHG}$ . The mirror current about 1/10800 of the blocking FET current will dump into the external resistor thru ICHG pin and compared to the internal reverence 1V. So $I_{CC} = (1V / R_{ICHG}) \times 10800$ , $R_{ICHG} \leq 42k\Omega$ . |

| NTC      | Thermal protection pin. Floating can disable charge logic and make the IC operate as normal boost regulator.                                                                                                                                                                                                  |

| BAT      | Battery positive pin.                                                                                                                                                                                                                                                                                         |

| BS       | Boost-Strap pin. Supply Rectified FET's gate driver. Decouple this pin to SW with 0.1 $\mu$ F ceramic cap.                                                                                                                                                                                                    |

| BD       | Connect to the Drain of internal Blocking FET. Bypass at least 4.7 $\mu$ F ceramic cap to GND.                                                                                                                                                                                                                |

| EN       | Enable control pin. High logic for enable on, and low logic for enable off.                                                                                                                                                                                                                                   |

| SYSRT    | System ON/OFF control pin. When VBAT is lower than 6V, SYSRT pin outputs low logic to turn off the system operation; when VBAT is high than 6V, SYSRT pin outputs high logic to turn on the system operation.                                                                                                 |

| SGND     | Signal ground pin.                                                                                                                                                                                                                                                                                            |

| PGND     | Power ground pin.                                                                                                                                                                                                                                                                                             |

## Absolute Maximum Ratings

Stresses beyond those listed under the Absolute Maximum Rating table may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                       | Rating     | Unit |

|-------------------------------------------------|------------|------|

| VIN, BAT, SW, NTC, STAT, BD, EN, ICHG, CV, ILIM | 18         | V    |

| TIM, SYSRT                                      | 6          | V    |

| BS-SW Voltage                                   | 6          | V    |

| SW Pin current continuous                       | 5          | A    |

| Junction Temperature Range                      | -40 to 125 | °C   |

| Lead Temperature                                | 260        | °C   |

| Storage Temperature Range                       | -60 to 150 | °C   |

## Recommend Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. DIOO does not recommend exceeding them or designing to absolute maximum ratings.

| Parameter                                  | Rating       | Unit |

|--------------------------------------------|--------------|------|

| VIN                                        | 4.375 to 5.5 | V    |

| BAT, SW, NTC, STAT, BD, EN, ICHG, CV, ILIM | -0.3 to 16   | V    |

| TIM, SYSRT                                 | -0.3 to 5.5  | V    |

| SW Pin current continuous                  | 5            | A    |

| Junction Temperature Range                 | -40 to 125   | °C   |

| Ambient Temperature Range                  | -40 to 85    | °C   |

## Electrical Characteristics

$V_S=5V$ ,  $V_{CM}=V_{OUT}=2.5V$ ,  $R_L=2k\Omega$ ,  $C_L=100pF$ ,  $T_A=25^\circ C$ , unless otherwise specified.

| Symbol                         | Parameter                                                  | Test Conditions                                   | Min   | Typ  | Max   | Unit      |

|--------------------------------|------------------------------------------------------------|---------------------------------------------------|-------|------|-------|-----------|

| <b>Bias Supply (VIN)</b>       |                                                            |                                                   |       |      |       |           |

| $V_{IN}$                       | Supply voltage                                             |                                                   | 4.375 |      | 16    | V         |

| $V_{UVLO}$                     | $V_{IN}$ under voltage lockout threshold                   | $V_{IN}$ rising and measured from $V_{IN}$ to GND |       | 2.8  |       | V         |

| $\Delta V_{UVLO}$              | $V_{IN}$ under voltage lockout hysteresis                  | Measured from $V_{IN}$ to GND                     |       | 100  |       | mV        |

| $V_{OVP}$                      | Input overvoltage protection                               | $V_{IN}$ rising and measured from $V_{IN}$ to GND | 6     |      |       | V         |

| $\Delta V_{OVP}$               | Input overvoltage protection hysteresis                    | Measured from $V_{IN}$ to GND                     |       | 0.5  |       | V         |

| <b>Quiescent Current</b>       |                                                            |                                                   |       |      |       |           |

| $I_{BAT}$                      | Battery discharge current                                  | Shutdown IC                                       |       | 7    |       | $\mu A$   |

| $I_{IN}$                       | Input quiescent current                                    | Disable Charge                                    |       | 0.2  |       | mA        |

| <b>Oscillator and PWM(TBD)</b> |                                                            |                                                   |       |      |       |           |

| $f_{SW}$                       | Switching frequency                                        |                                                   |       | 1000 |       | kHz       |

| $T_{MINOFF}$                   | Main N-FET minimum off time                                | With 16V rating                                   |       | 100  |       | ns        |

| $T_{MAXOFF}$                   | Main N-FET maximum off time                                | With 16V rating                                   |       | 30   |       | $\mu s$   |

| $T_{MINON}$                    | Main N-FET minimum on time                                 | With 16V rating                                   |       | 100  |       | ns        |

| <b>Power MOSFET</b>            |                                                            |                                                   |       |      |       |           |

| $R_{NFET\_M}$                  | $R_{DS(ON)}$ of Main N-FET                                 |                                                   |       | 50   |       | $m\Omega$ |

| $R_{NFET\_R}$                  | $R_{DS(ON)}$ of Rectified N-FET                            |                                                   |       | 35   |       | $m\Omega$ |

| $R_{NFET\_B}$                  | $R_{DS(ON)}$ of Blocking N-FET                             |                                                   |       | 35   |       | $m\Omega$ |

| <b>Voltage Regulation</b>      |                                                            |                                                   |       |      |       |           |

| $V_{CV}$                       | 2-Cell CV charge mode voltage                              | $V_{CV}<1V$                                       | 8.358 | 8.40 | 8.442 | V         |

|                                |                                                            | $V_{CV}>2V$                                       | 8.656 | 8.70 | 8.743 |           |

| $V_{CVH}$                      | High level logic for CV                                    |                                                   | 2     |      |       | V         |

| $V_{CVL}$                      | Low level logic for CV                                     |                                                   |       |      | 1     | V         |

| $\Delta V_{RCH}$               | 2-Cell Recharge Voltage                                    |                                                   |       | 200  |       | mV        |

| $V_{TRK}$                      | 2-cell TC charge mode battery voltage threshold            | $V_{BAT}$ rising edge threshold                   | 5.4   | 5.6  | 5.8   | V         |

| <b>Charge Current</b>          |                                                            |                                                   |       |      |       |           |

|                                | Internal charge current accuracy for Constant Current Mode | $I_{CC}=1080mA$                                   | -10%  |      | 10%   |           |

## DIO6833A

|                                       |                                                                 |                                    |       |       |                 |

|---------------------------------------|-----------------------------------------------------------------|------------------------------------|-------|-------|-----------------|

| I <sub>TERM</sub>                     | Termination current                                             | I <sub>CC</sub> =1080mA            | 108   |       | mA              |

| <b>Output Voltage OVP</b>             |                                                                 |                                    |       |       |                 |

| V <sub>OVP</sub>                      | Output voltage OVP threshold                                    |                                    | 105%  | 110%  | 115%            |

| <b>Input Current Limit</b>            |                                                                 |                                    |       |       |                 |

| V <sub>min</sub>                      | V <sub>IN</sub> limit voltage                                   | Float ILIM                         |       | 4.74  |                 |

|                                       |                                                                 | Pull low ILIM                      |       | 4.375 |                 |

|                                       |                                                                 | Pull high ILIM                     |       | 4.5   |                 |

| <b>Timer</b>                          |                                                                 |                                    |       |       |                 |

| T <sub>TC</sub>                       | V <sub>BAT</sub> <V <sub>TRK</sub> timeout                      | C <sub>TIM</sub> =330nF            | 0.425 | 0.5   | 0.575           |

| T <sub>STOP</sub>                     | Charge termination timeout                                      |                                    | 3.825 | 4.5   | 5.175           |

| T <sub>MC</sub>                       | Charge mode change delay time                                   |                                    |       | 30    |                 |

| T <sub>TERM</sub>                     | Termination delay time                                          |                                    |       | 30    |                 |

| T <sub>RCHG</sub>                     | Recharge time delay                                             |                                    |       | 30    |                 |

| <b>System ON/OFF Control</b>          |                                                                 |                                    |       |       |                 |

| V <sub>HYSRT</sub>                    | High logic of system ON/OFF control                             |                                    | 2.1   |       | V               |

| V <sub>LHSRT</sub>                    | Low logic of system ON/OFF control                              |                                    |       | 0.6   | V               |

| V <sub>HYSSYS</sub>                   | Hysteresis for positive and negative edge                       |                                    | 100   |       | mV              |

| <b>Linear charger Mode</b>            |                                                                 |                                    |       |       |                 |

| I <sub>LCHG</sub>                     | Battery Charger current when the blocking FET is in linear mode | V <sub>BAT</sub> <V <sub>TRK</sub> |       | 25%   | I <sub>CC</sub> |

| I <sub>LPK</sub>                      | Peak linear current when Battery is absent                      |                                    |       | 1     | A               |

| V <sub>BD</sub>                       | Bus voltage regulation                                          |                                    | 5.8   | 6     | 6.2             |

| <b>Enable ON/OFF Control</b>          |                                                                 |                                    |       |       |                 |

| V <sub>ENH</sub>                      | High level logic for enable control                             |                                    | 1.5   |       | V               |

| V <sub>ENL</sub>                      | Low level logic for enable control                              |                                    |       | 0.4   | V               |

| <b>Battery Thermal Protection NTC</b> |                                                                 |                                    |       |       |                 |

| T <sub>DET_RANGE</sub>                | Detected temperature range                                      | R <sub>NTC</sub> =10KΩ             | -5    | 50    | °C              |

| V <sub>NTC_HOT</sub>                  | High temperature detection voltage threshold                    | Battery temperature rise           |       | 0.108 | V               |

|                                       | High temperature detection voltage hysteresis                   | Battery temperature drop           |       | 30    | mV              |

| V <sub>NTC_COLD</sub>                 | Low temperature detection voltage threshold                     | Battery temperature drop           |       | 1.233 | V               |

|                                       | Low temperature detection voltage hysteresis                    | Battery temperature rise           |       | 80    | mV              |

**High Efficiency, 2A, Two-Cell Boost Li-Ion Battery Charger Preliminary Specification**

| Thermal Regulation And Thermal shutdown |                                         |                  |  |     |  |    |

|-----------------------------------------|-----------------------------------------|------------------|--|-----|--|----|

| $T_{REG}$                               | Thermal regulation threshold            |                  |  | 120 |  | °C |

| $T_{SD}$                                | Thermal shutdown temperature            | Rising Threshold |  | 160 |  | °C |

| $T_{SDHYS}$                             | Thermal shutdown temperature hysteresis |                  |  | 30  |  | °C |

Specifications subject to change without notice.

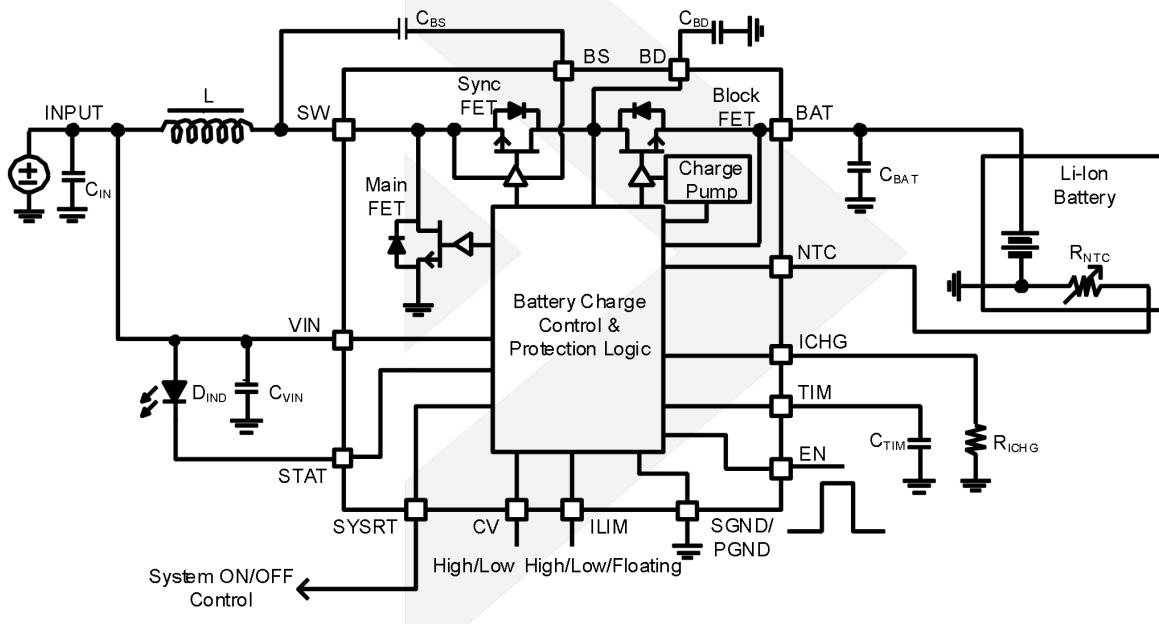

## Typical Applications

# General Function Description Operation

DIO6833A is a 4.375-5.5V, 2A two-cell synchronous boost Li-Ion battery charger integrates 1MHz switching frequency and full protection functions. The charge current up to 2A can be programmed by using the external resistor for different portable applications and indicates the charger current information simultaneous. It also has a programmable charge timeout and adaptive input current limit for safety battery charge operation. DIO6833A can disconnect output when there is output short circuit or shutdown happens. It consists of 18V rating FETs with extremely low ON resistance to achieve high charge efficiency and simple peripheral circuit design.

## Charging Status Indication Description

1. Charge-In-Process – Pull and keep STAT pin to Low;

2. Charge Done-Pull and keep STAT pin to High;

3. Fault Mode (UVLO, TSD, NTC error, timeout, BAT OVP)-Output high and low voltage alternatively with 1.3Hz frequency. Connect a LED from VIN to STAT pin, LED ON means Charge-in-Process, LED OFF means Charge Done, LED Flashing with 1.3Hz means Fault Mode.

## Switching Mode Boost Charger Basic Operation Description

### Switching Mode Control Strategy

DIO6833A is a switching mode Boost charger for the applications with USB power input. DIO6833A utilizes quasi-fixed frequency constant OFF time control to simplify the internal close-loop compensation design. Slope compensation is not necessary for the stable operation. The quasi-fixed frequency settled at 1MHz is easy for the size minimization of peripheral circuit design. During the light load operation, when the output voltage of the internal error amplifier VC is lower than the minimum threshold 0.3V, the OFF time is going to be stretched to achieve frequency fold back.

### Operation Principle

DIO6833A can normally work with or without Li-Ion battery both.

#### Battery Present

Before DIO6833A start-up, CBD is charged by the battery thru the body diode of blocking FET, and  $V_{BD}$  equals to  $V_{BAT}$ .

If the plug in input voltage  $V_{IN}$  is higher than  $V_{BD}=V_{BAT}$ , CBD is charged by  $V_{IN}$  further thru the body diode of sync-FET. Under this condition, the Boost charger operates in light load mode and regulates the  $V_{BD}$  at 6V and the blocking FET works in linear charge mode. Note that, charging current would not be increased to  $I_{CC}$  when the block FET operates in linear mode. With the increasing of  $V_{BAT}$ , when  $V_{BAT}$  is higher than both  $V_{IN}$  and  $V_{TRK}$  the blocking FET is fully turned on and the switching mode boost charger takes over the battery charging. The current in the blocking FET is mirrored to be as the charging current  $I_{CHG}$ . If  $V_{IN}$  is lower than  $V_{BD}=V_{BAT}$  at the plug in time, the switching mode boost charger starts work directly.

During the charging mode, constant (trickle) charging current loop is active first. When  $V_{BAT}$  equals to constant voltage threshold  $V_{CV}$ , constant voltage loop takes over and pull down the charging current. When  $I_{CHG}$  is lower than the termination current threshold  $I_{TERM}$ , the main FET of boost charger is turned off firstly. Sync-FET and blocking FETs are turned off together when the current is down to zero. Then, DIO6833A is waiting for recharge mode.

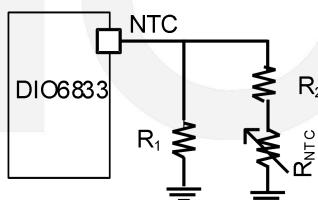

#### NTC protection

NTC pin output  $30\mu A$  current to NTC resistor ( $10k\Omega$ ). When battery temperature rises to  $50^\circ C$  ( $V_{NTC}=108mV$ ) or falls to  $-5^\circ C$  ( $V_{NTC}=1.233V$ ), the IC stops charging, and IC pulses the STAT pin. If NTC protection is not used, NTC pin should float or connect to  $10k\Omega$  normal resistor.

NTC protection temperature can be programmed by  $R_1$  and  $R_2$ , to get lower than  $-5^\circ C$  and higher than  $50^\circ C$  protection temperature.

The calculation methods are:

- 1) Get NTC resistor value  $R_{cold}$  at target cold temperature. Get NTC resistor value  $R_{hot}$  at target hot temperature.

Set  $R_c=41.1K$  and  $R_h=3.588K$

- 2) Calculate  $R_1$

$$R_1 = \frac{R_{\text{cold}} * R_C}{R_{\text{cold}} - R_C}$$

3) Calculate  $R_2$

$$R_2 = \frac{R_{\text{cold}} * R_h}{R_1 - R_h} - R_{\text{hot}}$$

If choose -8°C and 62°C protection, then  $R_{\text{cold}}=48.4\text{K}$  and  $R_{\text{hot}}=2.288\text{K}$  (for 10K\_3950RT NTC resistor).

Calculate result,

$R_1=272.5\text{K}$ ,  $R_2=1.35\text{K}$

Note: if  $R_1 < 160\text{K}$ , IC maybe not work at normal boost mode when removing battery and NTC resistor.

### Thermal Regulation and Protection

When the IC's junction temperature reaches  $T_{\text{REG}}$  (about 120°C), the charger reduces its output current to prevent overheating. If the temperature increases beyond  $T_{\text{SD}}$ ; charging is suspended, and STAT is pulsed. Charging resumes after the die cools to about 120°C.

### Battery Absent

If there's no battery connection detected thru NTC pin, DIO6833A operates as a normal switching mode boost converter and pulses STAT pin. When  $V_{\text{IN}}$  is higher than UVLO threshold, the blocking FET is softly turned on. After the blocking FET fully turn-on, switching mode boost converter starts work. The internal current loop and voltage loop are active both.

### Basic Protection Principle

DIO6833A has fully battery charging protection. When the input over voltage protection, the output over voltage protection, the thermal protection or the timeout protection happens, the main FET of the boost charger is turned off immediately. The sync-FET and the blocking FET are turned off later when the current is down to zero. When the  $V_{\text{BAT}}$  is lower than  $V_{\text{TRK}}$ , the short circuit protection happens. The main FET is turned off firstly. The block FET enters linear mode.

### Adaptive Input Current Limit Principle

DIO6833A has adaptive input current limit function. When the input voltage drops to  $V_{\text{INmin}}$ , input current and  $I_{\text{CHGREF}}$  will be reduced until input voltage recovers back.  $V_{\text{INmin}}$  is set by ILIM pin. Pull high for 4.5V, pull low for 4.375V, floating for 4.74V.

### Constant Voltage Threshold Program Principle

DIO6833A can program the constant voltage threshold thru the CV pin. When  $V_{\text{CV}}$  is higher than 2V, the constant voltage threshold is 8.7V; when  $V_{\text{CV}}$  is lower than 1V, the constant voltage threshold is 8.4V.

## Applications Information

Because of the high integration of DIO6833A, the application circuit based on this regulator IC is rather simple. Only input capacitor  $C_{IN}$ , output capacitor  $C_{OUT}$ , inductor L, and timer capacitor  $C_{TIM}$  need to be selected for the targeted applications specifications.

### Timer capacitor $C_{TIM}$

The charger also provides a programmable charge timer. The charge time is programmed by the capacitor connected between the TIM pin and GND. The capacitance is given by the formula:

$$C_{TM} = 2 * 10^{-11} T_{STOP} \quad \text{Unit: F}$$

$T_{STOP}$  is the target charge time, unit: s.

### Input capacitor $C_{IN}$

The ripple current through input capacitor is greater than

$$I_{CIN\_RMS} = \frac{V_{IN} * (V_{OUT} - V_{IN})}{2\sqrt{3} * L * F_{SW} * V_{OUT}}$$

X5R or X7R ceramic capacitors with greater than  $4.7\mu\text{F}$  capacitance are recommended to handle this ripple current.

### Output capacitor $C_{OUT}$

The output capacitor is selected to handle the output ripple noise requirements. This ripple voltage is related to the capacitance and its equivalent series resistance (ESR). For the best performance, it is recommended to use X5R or better grade low ESR ceramic capacitor. The voltage rating of the output capacitor should be higher than the maximum output voltage. The minimum required capacitance can be calculated as:

$$C_{OUT} = \frac{I_{CC} * (V_{OUT} - V_{IN})}{F_{SW} \times V_{OUT} \times V_{RIPPLE}}$$

$V_{RIPPLE}$  is the peak to peak output ripple;  $I_{CC}$  is the setting charge current.

For DIO6833A, output capacitor is paralleled by CBD and CBAT, for smaller output ripple noise, each capacitor with greater than  $10\mu\text{F}$  capacitance is recommended.

### Inductor L

There are several considerations in choosing this inductor.

- 1) Choose the inductance to provide the desired ripple current. It is suggested to choose the ripple current to be about 40% of the average input current. The inductance is calculated as:

$$L = \left( \frac{V_{IN}}{V_{OUT}} \right)^2 \frac{(V_{OUT} - V_{IN})}{I_{CC} \times F_{SW} \times 40\%}$$

Where FSW is the switching frequency and  $I_{CC}$  is the setting charge current.

The DIO6833A is quite tolerant of different ripple current amplitude. Consequently, the final choice of

inductance can be slightly off the calculation value without significantly impacting the performance.

- 2) The saturation current rating of the inductor must be selected to be greater than the peak inductor current under full load conditions.

$$I_{SAT, MIN} > \left( \frac{V_{OUT}}{V_{IN}} \right) \times I_{CC} + \left( \frac{V_{IN}}{V_{OUT}} \right)^2 \frac{(V_{OUT} - V_{IN})}{2 \times F_{SW} \times L}$$

- 3) The DCR of the inductor and the core loss at the switching frequency must be low enough to achieve the desired efficiency requirement. It is desirable to choose an inductor with DCR<10mohm to achieve a good overall efficiency.

### Layout Design

The layout design of DIO6833A regulator is relatively simple. For the best efficiency and minimum noise problems, we should place the following components close to the IC:  $C_{VIN}$ , L, and  $C_{BD}$ .

- 1) The loop of main MOSFET, rectifier diode, and  $C_{BD}$  must be as short as possible.

- 2) It is desirable to maximize the PCB copper area connecting GND pin to achieve the best thermal and noise performance.

- 3)  $C_{VIN}$  must be close to pin VIN and GND.

- 4) The PCB copper area associated with SW pin must be minimized to avoid the potential noise problem.

- 5) The small signal component  $R_{ICHG}$  must be placed close to IC and must not be adjacent to the SW net on the PCB layout to avoid the noise problem.

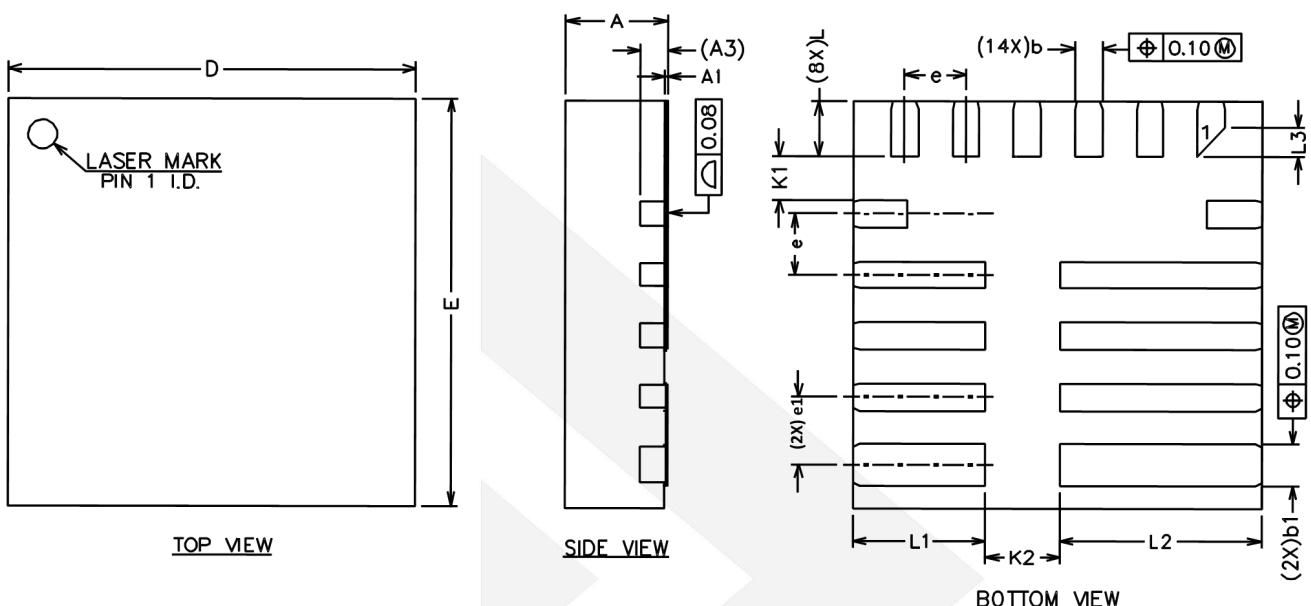

## Physical Dimensions: QFN3\*3-16

| COMMON DIMENSIONS<br>(UNITS OF MEASURE=MILLIMETER) |         |       |       |

|----------------------------------------------------|---------|-------|-------|

| Symbol                                             | MIN     | NOM   | MAX   |

| A                                                  | 0.70    | 0.75  | 0.80  |

| A1                                                 | 0.00    | 0.02  | 0.05  |

| A3                                                 | 0.20REF |       |       |

| b                                                  | 0.15    | 0.20  | 0.25  |

| b1                                                 | 0.25    | 0.30  | 0.35  |

| D                                                  | 2.90    | 3.00  | 3.10  |

| E                                                  | 2.90    | 3.00  | 3.10  |

| e                                                  | 0.35    | 0.45  | 0.55  |

| e1                                                 | 0.40    | 0.50  | 0.60  |

| L                                                  | 0.35    | 0.40  | 0.45  |

| L1                                                 | 0.92    | 0.97  | 1.02  |

| L2                                                 | 1.43    | 1.48  | 1.53  |

| L3                                                 | -       | 0.214 | -     |

| K1                                                 | 0.225   | 0.325 | 0.425 |

| K2                                                 | 0.45    | 0.55  | 0.65  |

## CONTACT US

Dioo is a professional design and sales corporation for high-quality and performance analog semiconductors. The company focuses on industry markets, such as cell phones, handheld products, laptops, medical equipment, and so on. Dioo's product families include analog signal processing and amplifying, LED drivers, and charger ICs. Go to <http://www.dioo.com> for a complete list of Dioo product families.

For additional product information or full datasheet, please contact our sales department or representatives.