## DIO5008

# DP/DM Dual SPDT Switch with 20 V Overvoltage Protection

## Features

- Operating voltage range: 2.3 V to 5.5 V

- Differential 2:1 or 1:2 switch/multiplexer

- $V_{CC} = 0$  V powered off protection

- Low  $R_{ON}$ : 5.5  $\Omega$

- Bandwidth: 1.5 GHz

- $C_{ON}$ : 4.5 pF

- Overvoltage protection (OVP) on common pins up to 20 V DC

- Temperature range of -40°C to 85°C

- Package: QFN2\*1.5-10 and DQFN1.8\*1.4-10

## Descriptions

The DIO5008 is a high-speed USB 2.0 low-power dual SPDT, analog switch with overvoltage protection. The device is configured as a dual 2:1 or 1:2 switch and is optimized for handling the USB 2.0 D+/- lines in a USB Type-C system.

The DIO5008 protects the system components behind the switch with over-voltage fault protection up to 20 V.

The DIO5008 is available in QFN2\*1.5-10 and DQFN1.8\*1.4-10 packages, which makes it a perfect solution for mobile applications.

## Applications

- Mobiles

- PC/Notebooks

- Tablets

- USB Type-C

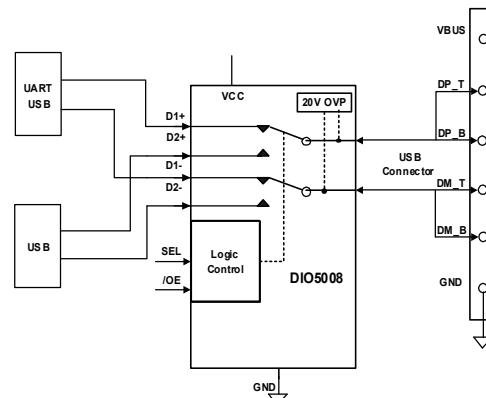

## Simplified Schematic

## Ordering Information

| Part Number | Top Marking | RoHS  | $T_A$       | Package        |                   |

|-------------|-------------|-------|-------------|----------------|-------------------|

| DIO5008QN10 | YW5H        | Green | -40 to 85°C | QFN2*1.5-10    | Tape & Reel,3000  |

| DIO5008LP10 | YW5H        | Green | -40 to 85°C | DQFN1.8*1.4-10 | Tape & Reel, 3000 |

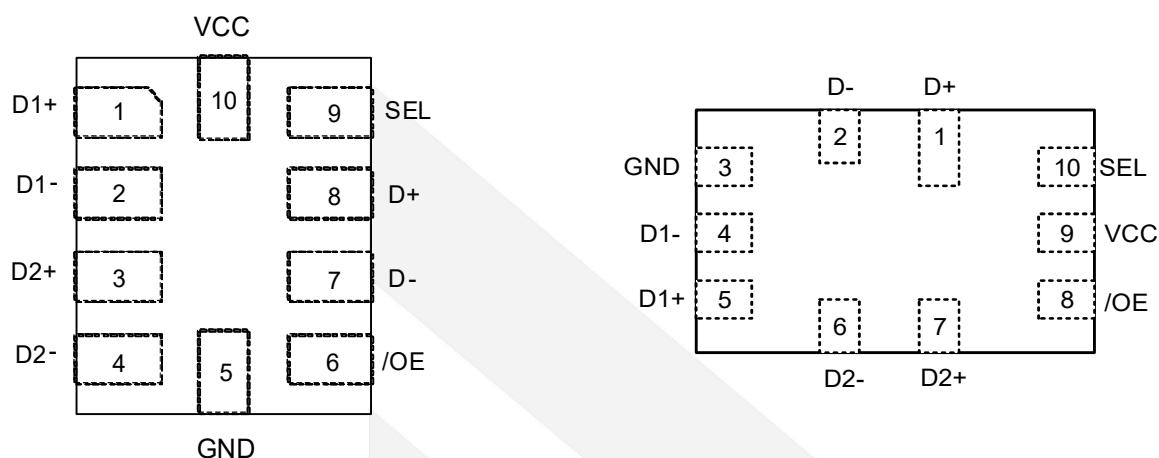

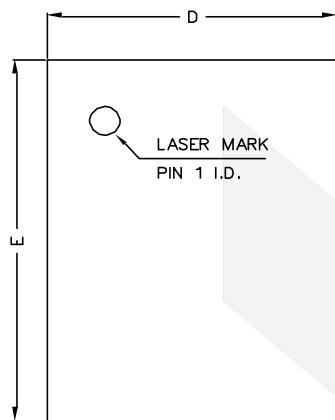

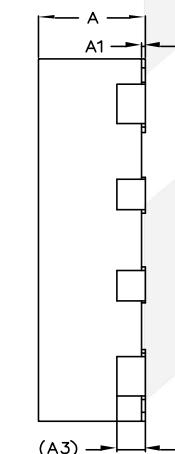

## Pin Assignments

**QFN2\*1.5-10**

**DQFN1.8\*1.4-10**

**Figure 1. Top View**

## Pin Description

| Pin Name | Direction | Description                                                           |

|----------|-----------|-----------------------------------------------------------------------|

| D1+      | I/O       | USB1 data link (differential+)                                        |

| D1-      | I/O       | USB1 data link (differential-)                                        |

| D2+      | I/O       | USB2 data link (differential+)                                        |

| D2-      | I/O       | USB2 data link (differential-)                                        |

| GND      | -         | Ground                                                                |

| /OE      | I         | Output enable (active low)                                            |

| D-       | I/O       | Switch output (differential-)                                         |

| D+       | I/O       | Switch output (differential+)                                         |

| SEL      | I         | Switch selection<br>(LOW = D+/D- To D1+/D1-, HIGH = D+/D- To D2+/D2-) |

| VCC      | -         | Power supply pin                                                      |

**DIO5008**

## Absolute Maximum Ratings

Stresses beyond those listed under the Absolute Maximum Rating table may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol    | Parameter                                                                     | Min  | Max | Unit |

|-----------|-------------------------------------------------------------------------------|------|-----|------|

| $V_{CC}$  | Supply voltage <sup>(1)</sup>                                                 | -0.5 | 6   | V    |

| $V_{I/O}$ | Input /output DC voltage (D+,D-) <sup>(1)</sup>                               | -0.5 | 28  | V    |

| $V_{I/O}$ | Input /output DC voltage (D1+/D1-, D2+/D2-) <sup>(1)</sup>                    | -0.5 | 6   | V    |

| $V_I$     | Digital input voltage (SEL, /OE)                                              | -0.5 | 6   | V    |

| $I_K$     | Input-output port diode current (D+, D-, D1+, D1-, D2+, D2-) ( $V_{IN} < 0$ ) | -50  |     | mA   |

| $I_{IK}$  | Digital logic input clamp current (SEL, /OE) <sup>(1)</sup> ( $V_I < 0$ )     | -50  |     | mA   |

| $I_{CC}$  | Continuous current through $V_{CC}$                                           |      | 100 | mA   |

| $I_{GND}$ | Continuous current through GND                                                | -100 |     | mA   |

| $T_{stg}$ | Storage temperature                                                           | -65  | 150 | °C   |

(1) All voltages are with respect to ground, unless otherwise specified.

## Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. DIOO does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol                            | Parameter                                   | Rating    | Unit |

|-----------------------------------|---------------------------------------------|-----------|------|

| $V_{CC}$                          | Supply voltage                              | 2.3 ~ 5.5 | V    |

| $V_{I/O}$ (D+, D-)                | Analog input/output voltage                 | 0 ~ 20    | V    |

| $V_{I/O}$ (D1+, D1-, D2+, D2-)    |                                             | 0 ~ 3.6   | V    |

| $V_I$                             | Digital input voltage (SEL, /OE)            | 0 ~ 5.5   | V    |

| $I_{I/O}$ (D+,D-,D1+,D1-,D2+,D2-) | Analog input/output port continuous current | -50 ~ 50  | mA   |

| $I_{OL}$                          | Digital output current                      | 3         | mA   |

| $T_A$                             | Operating free-air temperature              | -40 ~ 85  | °C   |

| $T_J$                             | Junction temperature                        | -40 ~ 125 | °C   |

DIO5008

## Electrical Characteristics

$T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $V_{CC} = 2.3\text{ V}$  to  $5.5\text{ V}$ ,  $GND = 0\text{ V}$ , typical values are at  $V_{CC} = 3.3\text{ V}$ ,  $T_A = 25^\circ\text{C}$ , (unless otherwise noted)

| Symbol                         | Parameter                                         | Test Conditions                                                                                                                                                                       | Min  | Typ | Max  | Unit          |

|--------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|---------------|

| <b>Supply</b>                  |                                                   |                                                                                                                                                                                       |      |     |      |               |

| $V_{CC}$                       | Power supply voltage                              |                                                                                                                                                                                       | 2.3  |     | 5.5  | V             |

| $I_{CC}$                       | Active supply current                             | $/OE = 0\text{ V}$ , $SEL = 0\text{ V}$ , $1.2\text{ V}$ , $1.8\text{ V}$ or $V_{CC}$<br>$V_{CC} \leq 4.4\text{ V}$ , $0\text{ V} < V_{I/O} < 3.6\text{ V}$                           |      | 26  | 37   | $\mu\text{A}$ |

|                                | Supply current during OVP condition               | $/OE = 0\text{ V}$ , $SEL = 0\text{ V}$ , $1.2\text{ V}$ , $1.8\text{ V}$ or $V_{CC}$<br>$V_{CC} \leq 4.4\text{ V}$ , $V_{I/O} > V_{OVP\_TH}$                                         |      | 26  | 37   | $\mu\text{A}$ |

| $I_{CC\_PD}$                   | Standby powered down supply current               | $/OE = 1.2\text{ V}$ , $1.8\text{ V}$ or $V_{CC}$ ,<br>$SEL = 0\text{ V}$ , $1.2\text{ V}$ , $1.8\text{ V}$ , or $V_{CC}$                                                             |      | 1.5 | 10   | $\mu\text{A}$ |

| <b>DC Characteristics</b>      |                                                   |                                                                                                                                                                                       |      |     |      |               |

| $R_{ON}$                       | ON-state resistance                               | $V_{I/O} = 0.4\text{ V}$ , $I_{SINK} = 8\text{ mA}$<br>Refer to ON-state resistance figure                                                                                            |      | 5.5 | 9    | $\Omega$      |

| $\Delta R_{ON}$                | ON-state resistance match between channels        | $V_{I/O} = 0.4\text{ V}$ , $I_{SINK} = 8\text{ mA}$<br>Refer to ON-state resistance figure                                                                                            |      |     | 0.3  | $\Omega$      |

| $R_{ON\text{ (FLAT)}}$         | ON-state resistance match flatness                | $V_{I/O} = 0\text{ V}$ to $0.4\text{ V}$ , $I_{SINK} = 8\text{ mA}$<br>Refer to ON-state resistance figure                                                                            |      | 0.1 | 0.4  | $\Omega$      |

| $I_{OFF}$                      | I/O pin OFF leakage current                       | $V_{D\pm} = 0\text{ V}$ or $3.6\text{ V}$ , $V_{CC} = 2.3\text{ V}$ to $5.5\text{ V}$<br>$V_{D1\pm}$ or $V_{D2\pm/-} = 3.6\text{ V}$ or $0\text{ V}$ ,<br>Refer to OFF leakage figure | -1   | 0.5 | 2    | $\mu\text{A}$ |

|                                |                                                   | $V_{D\pm} = 0\text{ V}$ or $20\text{ V}$ , $V_{CC} = 2.3\text{ V}$ to $5.5\text{ V}$<br>$V_{D1\pm}$ or $V_{D2\pm/-} = 0\text{ V}$ ,<br>Refer to OFF leakage figure                    | -1   | 149 | 200  | $\mu\text{A}$ |

| $I_{ON}$                       | ON leakage current                                | $V_{D\pm} = 0\text{ V}$ or $3.6\text{ V}$ ,<br>$V_{D1\pm}$ and $V_{D2\pm/-} = \text{High-Z}$<br>Refer to ON leakage figure                                                            | -1   | 0.5 | 2    | $\mu\text{A}$ |

| $Z_{ON}$                       | ON state impedance to GND                         |                                                                                                                                                                                       | 5    | 8   |      | $M\Omega$     |

| <b>Digital Characteristics</b> |                                                   |                                                                                                                                                                                       |      |     |      |               |

| $V_{IH}$                       | Input logic high                                  | $SEL$ , $/OE$                                                                                                                                                                         | 0.85 |     |      | V             |

| $V_{IL}$                       | Input logic low                                   | $SEL$ , $/OE$                                                                                                                                                                         |      |     | 0.45 | V             |

| $I_{IH}$                       | Input high leakage current                        | $SEL$ , $/OE = 1.2\text{ V}$ , $1.8\text{ V}$ , $V_{CC}$                                                                                                                              | -1   | 0.5 | 5    | $\mu\text{A}$ |

| $I_{IL}$                       | Input low leakage current                         | $SEL$ , $/OE = 0\text{ V}$                                                                                                                                                            | -1   | 0   | 5    | $\mu\text{A}$ |

| $R_{PD}$                       | Internal pull-down resistor on digital input pins |                                                                                                                                                                                       |      | 6   |      | $M\Omega$     |

| $C_I$                          | Digital input capacitance                         | $SEL = 0\text{ V}$ , $1.2\text{ V}$ , $1.8\text{ V}$ or $V_{CC}$ ,<br>$f = 1\text{ MHz}$                                                                                              |      | 3.4 |      | $\text{pF}$   |

**DP/DM Dual-SPDT Switch with 20 V Overvoltage Protection**

## DIO5008

# DP/DM Dual-SPDT Switch with 20 V Overvoltage Protection

### Protection

|                   |                                                                                |                                                                                                                                              |     |     |     |    |

|-------------------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| $V_{OVP\_TH}$     | OVP positive threshold                                                         |                                                                                                                                              | 4.8 | 5.1 | 5.4 | V  |

| $V_{OVP\_HYS\_T}$ | OVP threshold hysteresis                                                       |                                                                                                                                              | 75  | 230 | 425 | mV |

| $V_{CLAMP\_V}$    | Maximum voltage to appear on D1 $\pm$<br>And D2 $\pm$ pins during OVP scenario | $V_{D\pm} = 0$ to 16 V<br>$t_{RISE}$ and $t_{FALL}(10\% \text{ to } 90\%) = 100$ ns<br>$R_L = \text{open}$ , switch ON or OFF<br>$/OE = 0$ V | 0   |     | 9   | V  |

|                   |                                                                                | $V_{D\pm} = 0$ to 16 V<br>$t_{RISE}$ and $t_{FALL}(10\% \text{ to } 90\%) = 100$ ns<br>$R_L = 50 \Omega$ , switch ON or OFF<br>$/OE = 0$ V   | 0   |     | 9   | V  |

## DIO5008

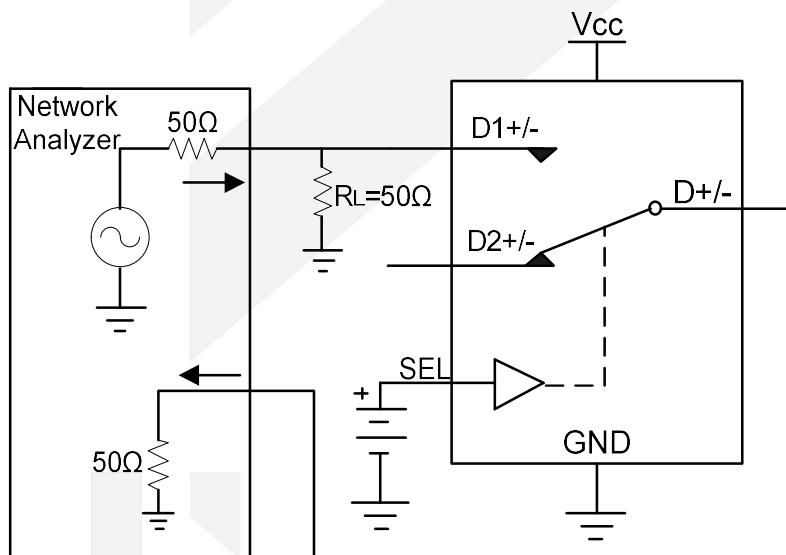

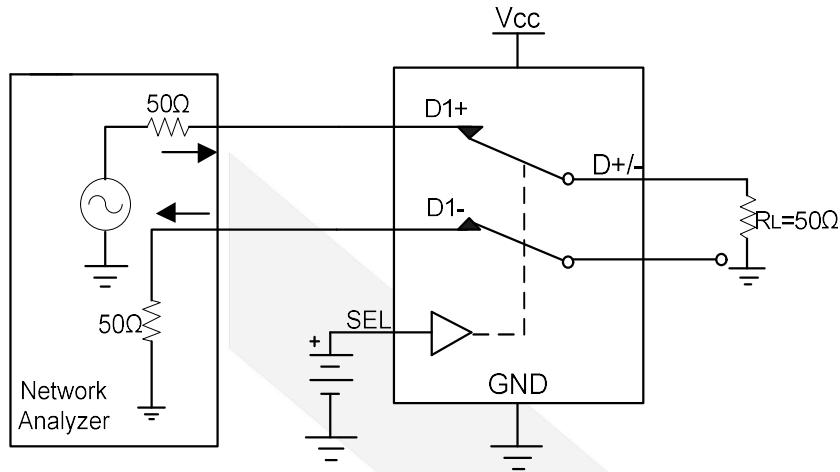

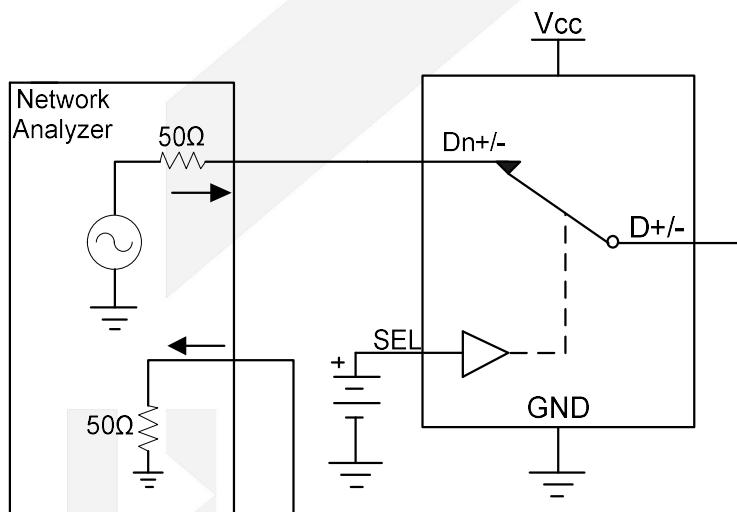

### Dynamic Characteristics

$T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $V_{CC} = 2.3\text{ V}$  to  $5.5\text{ V}$ ,  $GND = 0\text{ V}$ , typical values are at  $V_{CC} = 3.3\text{ V}$ ,  $T_A = 25^\circ\text{C}$ , (unless otherwise noted)

| Symbol     | Parameter              | Test Conditions                                                                                                      | Min | Typ | Max | Unit |

|------------|------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $C_{OFF}$  | D+, D- OFF capacitance | $V_{D+/-} = 0$ or $3.3\text{ V}$ , $/OE = V_{CC}$<br>$f = 240\text{ MHz}$ , switch OFF                               | 1.2 | 3.5 | 6.2 | pF   |

| $C_{ON}$   | IO pins ON capacitance | $V_{D+/-} = 0$ or $3.3\text{ V}$ , $f = 240\text{ MHz}$<br>switch ON                                                 | 1.4 | 4.5 | 6.2 | pF   |

| $O_{ISO}$  | OFF isolation          | $R_L = 50\text{ }\Omega$ , $C_L = 5\text{ pF}$ , $f = 240\text{ MHz}$<br>Refer to OFF isolation figure<br>switch OFF |     | -30 |     | dB   |

| $X_{TALK}$ | Crosstalk              | $R_L = 50\text{ }\Omega$ , $C_L = 5\text{ pF}$ , $f = 100\text{ kHz}$<br>Refer to crosstalk figure<br>switch ON      |     | -90 |     | dB   |

| BW         | Bandwidth              | $R_L = 50\text{ }\Omega$<br>Refer to BW and insertion loss figure<br>switch ON                                       |     | 1.5 |     | GHz  |

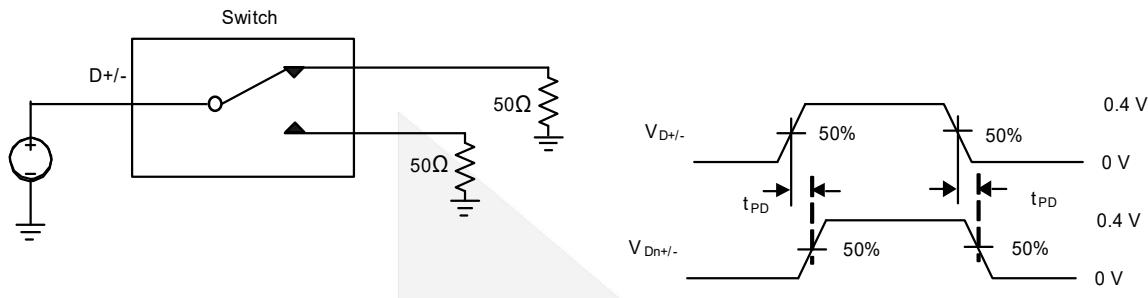

### Timing Requirements

$T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$ ,  $V_{CC} = 2.3\text{ V}$  to  $5.5\text{ V}$ ,  $GND = 0\text{ V}$ , typical values are at  $V_{CC} = 3.3\text{ V}$ ,  $T_A = 25^\circ\text{C}$ , (unless otherwise noted)

| Symbol       | Parameter                                       | Test Conditions                                | Min                                                                                              | Typ  | Max | Unit          |

|--------------|-------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-----|---------------|

| $t_{switch}$ | Switching time between channels (SEL to output) | $V_{D+/-} = 0.8\text{ V}$<br>Refer to figure 5 |                                                                                                  | 0.6  |     | $\mu\text{s}$ |

| $t_{ON}$     | Device turn ON time ( $/OE$ to output)          | $V_{D+/-} = 0.8\text{ V}$<br>Refer to figure 6 | $R_L = 50\text{ }\Omega$ ,<br>$C_L = 5\text{ pF}$ ,<br>$V_{CC} = 2.3\text{ V}$ to $5.5\text{ V}$ | 130  |     | $\mu\text{s}$ |

| $t_{OFF}$    | Device turn OFF time ( $/OE$ to output)         | $V_{D+/-} = 0.8\text{ V}$<br>Refer to figure 6 |                                                                                                  | 0.05 |     | $\mu\text{s}$ |

## Application Information

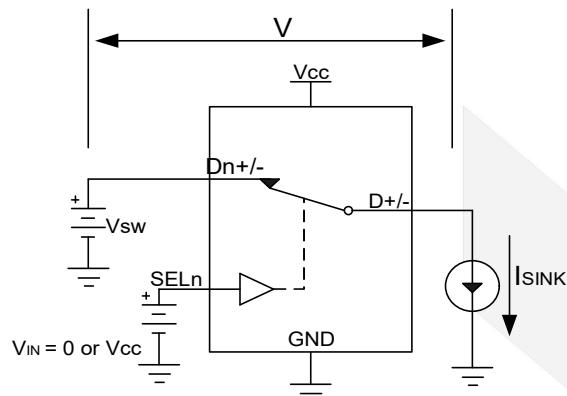

Channel on,  $R_{ON} = V/I_{SINK}$

**Figure 2. ON-state resistance ( $R_{ON}$ )**

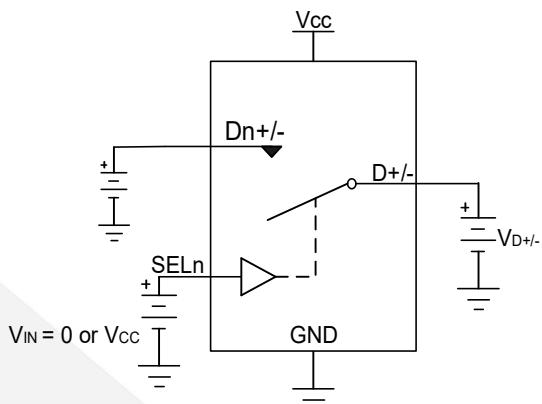

**Figure 3. OFF leakage**

**Figure 4. ON leakage**

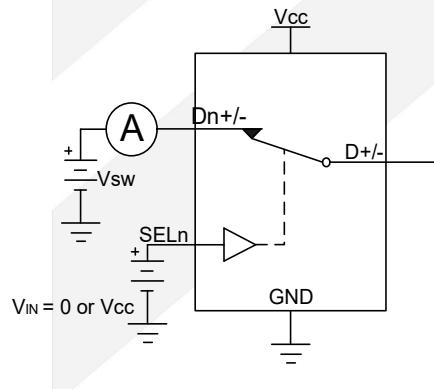

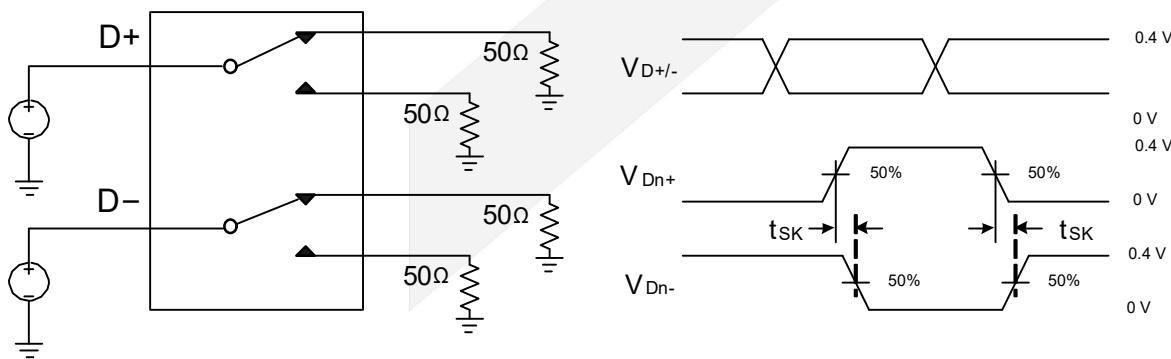

- (1) All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ ,  $t_r < 500 \text{ ps}$ ,  $t_f < 500 \text{ ps}$ .

- (2)  $C_L$  includes probe and jig capacitance.

**Figure 5.  $t_{SWITCH}$  Timing**

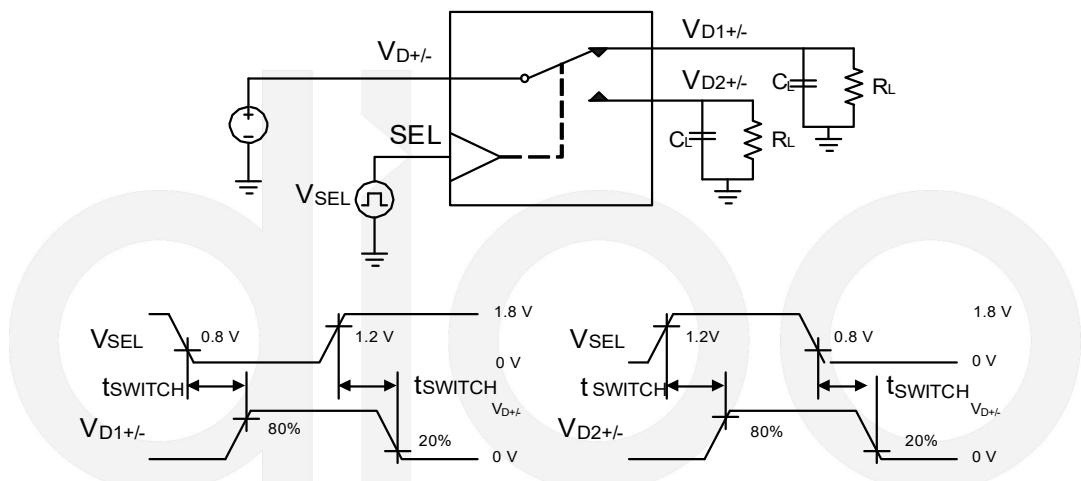

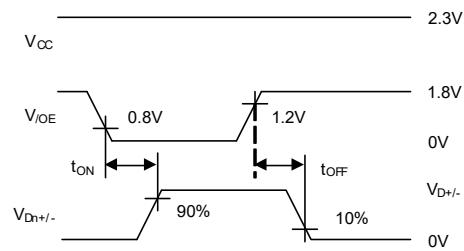

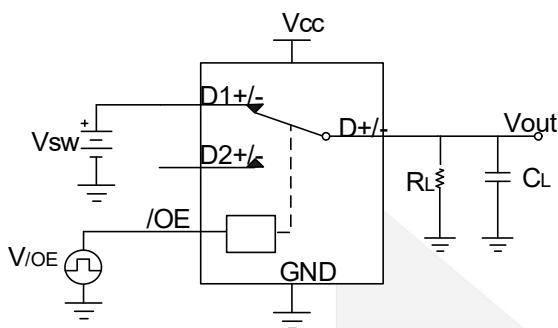

- (1) All input pulses are supplied by generators having the following characteristics: PRR $\leq$ 10MHz,  $Z_O=50\Omega$ ,  $t_r<500\text{ps}$ ,  $t_f<500\text{ps}$ .

- (2)  $C_L$  includes probe and jig capacitance.

**Figure 6.  $t_{ON}$ ,  $t_{OFF}$  for /OE**

**Figure 7. OFF Isolation**

**Figure 8. Crosstalk**

**Figure 9. BW and insertion loss**

- (1) All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10MHz,  $Z_O = 50 \Omega$ ,  $t_r < 500$  ps,  $t_f < 500$  ps.

- (2)  $C_L$  includes probe and jig capacitance.

**Figure 10.  $t_{PD}$**

- (1) All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  10 MHz,  $Z_O = 50 \Omega$ ,  $t_r < 500$  ps,  $t_f < 500$  ps.

- (2)  $C_L$  includes probe and jig capacitance.

**Figure 11.  $t_{SK}$**

## Detailed Description

### Overview

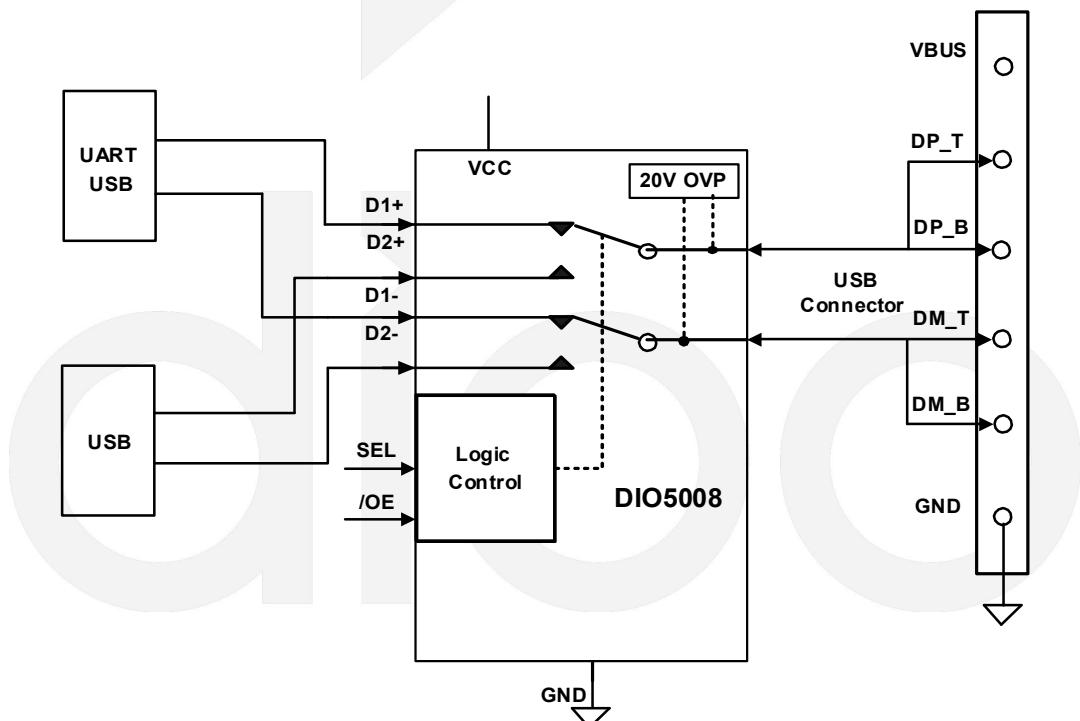

The DIO5008 is a bidirectional low-power, dual port, high-speed, USB 2.0 analog switch with an integrated protection for USB Type-C systems. The device is configured as a dual 2:1 or 1:2 switch and is optimized for handling the USB 2.0 D+/- lines in a USB Type-C system as shown in Figure 12.

| A1  | A2   | A3   | A4 | A5   | A6 | A7 | A8   | A9 | A10  | A11  | A12 |

|-----|------|------|----|------|----|----|------|----|------|------|-----|

| GND | TX1+ | TX1- | +V | CC1  | D+ | D- | SBU1 | +V | RX2- | RX2+ | GND |

| GND | RX1+ | RX1- | +V | SBU2 | D- | D+ | CC2  | +V | TX2- | TX2+ | GND |

| B12 | B11  | B10  | B9 | B8   | B7 | B6 | B5   | B4 | B3   | B2   | B1  |

USB3.1 Super speed+ 10 Gbps

Secondary Bus

USB2.0 High speed 480 Mbps

USB Power Delivery Communication

**Figure 12. USB Type-C Connector Pinout**

The DIO5008 also works in traditional USB systems that need protection from fault conditions such as automotive and applications that require higher voltage charging. The device maintains excellent signal integrity through the optimization of both  $R_{ON}$  and BW while protecting the system with 0 V to 20 V OVP protection. The OVP implementation is designed to protect sensitive system components behind the switch that cannot survive a fault condition where VBUS is shorted the D+ and D- pins on the connector.

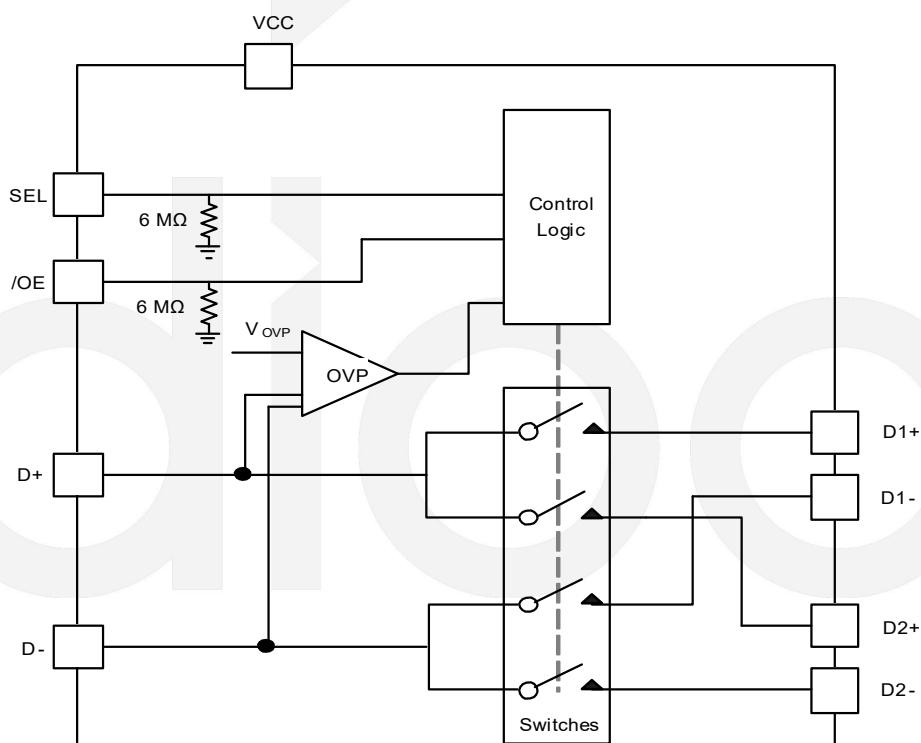

### Functional Block Diagram

## Feature Description

### Powered-off Protection

When the DIO5008 is powered off, the I/Os of the device remain in a high-Z state. The crosstalk, off-isolation, and leakage remain within the Electrical Specifications.

This prevents errant voltages from reaching the rest of the system and maintains isolation when the system is powered up.

### Overvoltage Protection

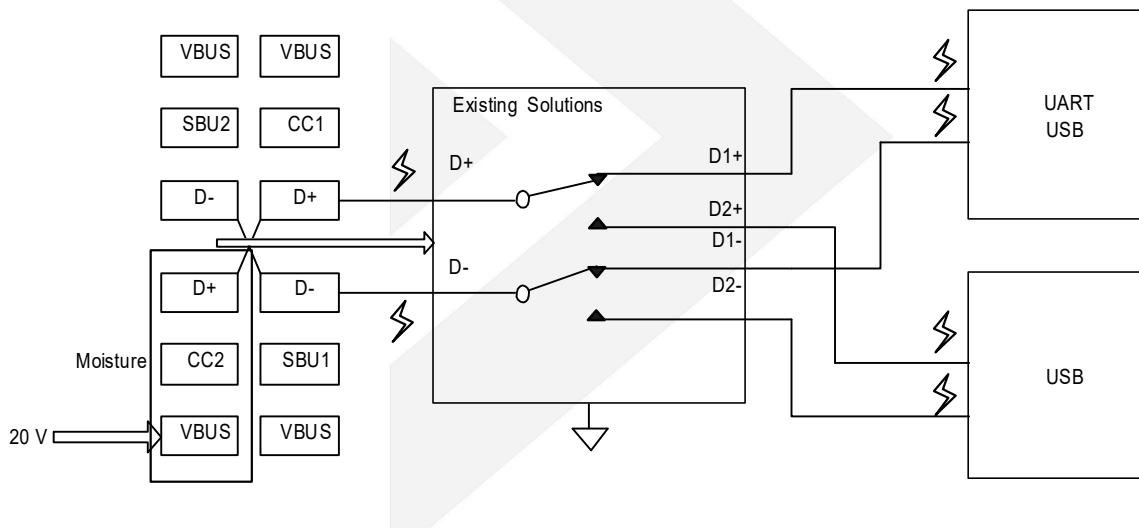

The OVP of the DIO5008 is designed to protect the system from D+/- shorts to VBUS at the USB and USB Type-C connectors. Figure 13 depicts a moisture short that would cause 20 V to appear on an existing USB solution that could pass through the device and damage components behind the device.

Figure 13. Existing solution being damaged by a short, 20 V

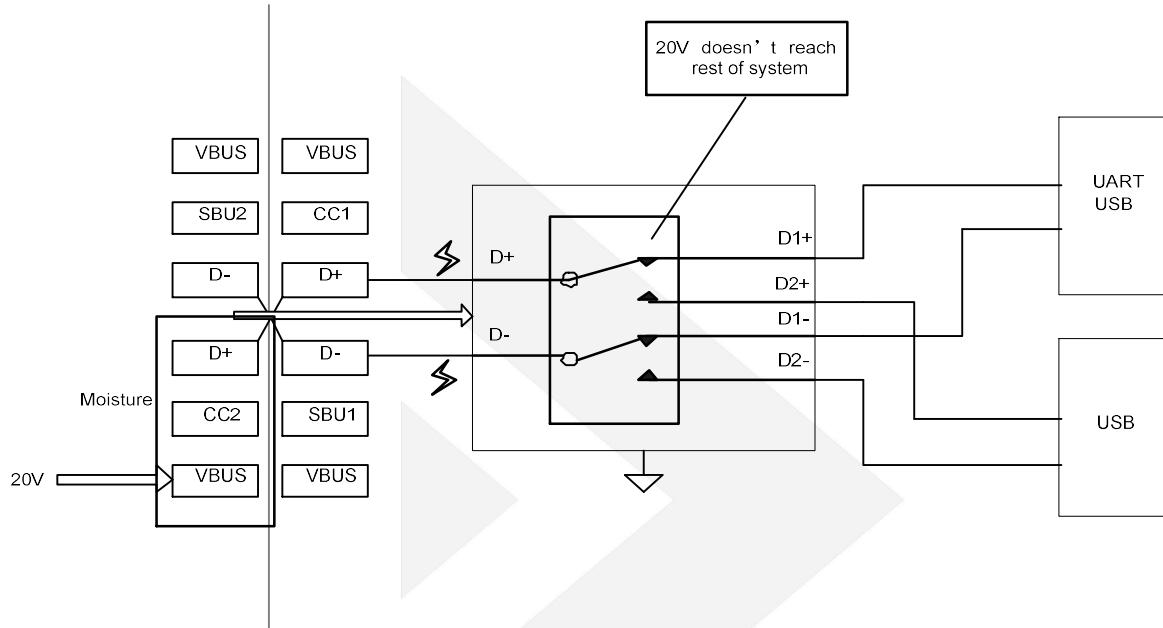

The DIO5008 will open the switches and protect the rest of the system by blocking the 20 V as depicted in Figure 14.

**Figure 14. Protecting During a 20 V Short**

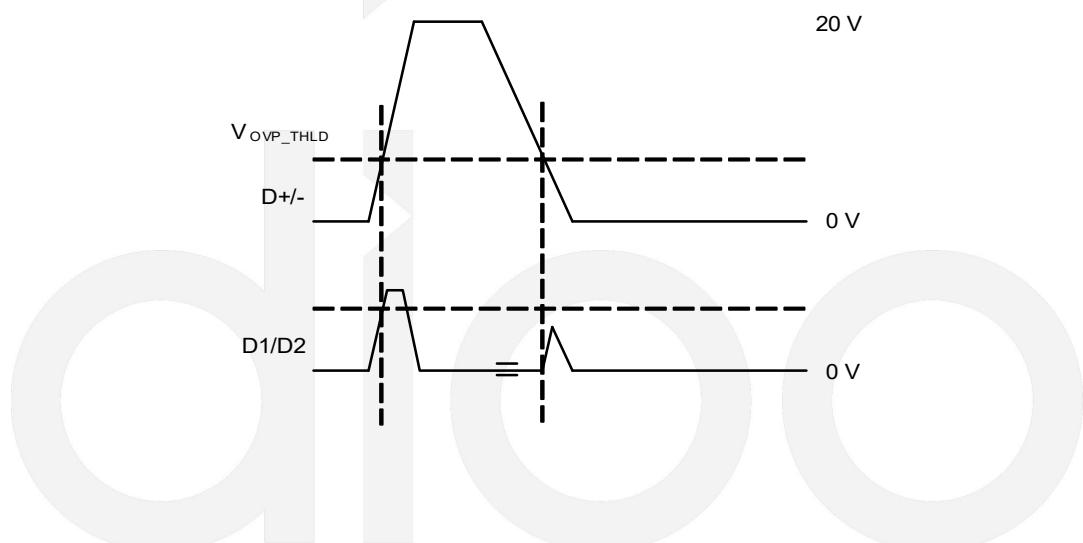

Figure 15 is a waveform showing the voltage on the pins during an over-voltage scenario.

**Figure 15. Overvoltage Protection Waveform, 20 V**

**Device Functional Modes**

**Pin Functions**

**Table 1. Function Table**

| /OE | SEL | D- Connection | D+ Connection |

|-----|-----|---------------|---------------|

| H   | X   | High-Z        | High-Z        |

| L   | L   | D- to D1-     | D+ to D1+     |

| L   | H   | D- to D2-     | D+ to D2+     |

## Application and Implementation

**Application Information**

There are many USB applications in which the USB hubs or controllers have a limited number of USB I/Os or need to route signals from a single USB connector. The DIO5008 solution can effectively expand the limited USB I/Os by switching between multiple USB buses to interface them to a single USB hub or controller or route signals from one connector to two different locations.

**Typical Application**

The DIO5008 is used to switch signals between the USB path, which goes to the base band or application processor, and the UART path, which goes to debug port. The DIO5008 has internal 6 MΩ pull-down resistors on SEL and /OE. The pull-down on SEL ensures the D1+/D1- channel is selected by default. The pull-down on /OE enables the switch when power is applied.

**Figure 16. Typical DIO5008 Application**

## Design Requirements

Design requirements of USB 1.0, 1.1, and 2.0 standards must be followed. The DIO5008 has internal  $6\text{ M}\Omega$  pull-down resistors on SEL and /OE, so no external resistors are required on the logic pins. The internal pull-down resistor on SEL ensures the D1+ and D1- channels are selected by default. The internal pull-down resistor on /OE enables the switch when power is applied to VCC.

## Detailed Design Procedure

The DIO5008 can be properly operated without any external components. However, unused pins must be connected to the ground through a  $50\text{ }\Omega$  resistor to prevent signal reflections back into the device. Place a  $100\text{ nF}$  bypass capacitor close to the DIO5008 VCC pin.

## Power Supply Recommendations

Power to the device is supplied through the VCC pin and must follow the USB 1.0, 1.1, and 2.0 standards. Place a  $100\text{ nF}$  bypass capacitor as close to the supply pin VCC as possible to help smooth out lower frequency noise to provide better load regulation across the frequency spectrum.

## Layout

### Layout Guidelines

1. Place supply bypass capacitors as close to the VCC pin as possible and avoid placing the bypass caps near the D $\pm$  traces.

2. The high-speed D $\pm$  must match and be no more than 4 inches long; otherwise, the eye diagram performance may be degraded. A high-speed USB connection is made through a shielded, twisted pair cable with a differential characteristic impedance. In layout, the impedance of D+ and D- traces must match the cable characteristic differential impedance for optimal performance.

3. Route the high-speed USB signals by using a minimum of vias and corners to reduce signal reflections and impedance changes. When a via must be used, increase the clearance size around it to minimize its capacitance. Each via introduces discontinuities in the signal's transmission line and increases the chance of picking up interference from the other layers of the board. Be careful when designing test points on twisted pair lines; through-hole pins are not recommended.

4. When it becomes necessary to turn  $90^\circ$ , use two  $45^\circ$  turns or an arc instead of making a single  $90^\circ$  turn. This practice reduces reflections on the signal traces by minimizing impedance discontinuities.

5. Do not route USB traces under or near crystals, oscillators, clock signal generators, switching regulators, mounting holes, magnetic devices, or ICs that use or duplicate clock signals.

6. Avoid stubs on high-speed USB signals because they cause signal reflections. If a stub is unavoidable, then the stub must be less than 200 mm.

7. Route all high-speed USB signal traces over continuous GND planes, with no interruptions.

8. Avoid crossing over anti-etch, commonly found with plane splits.

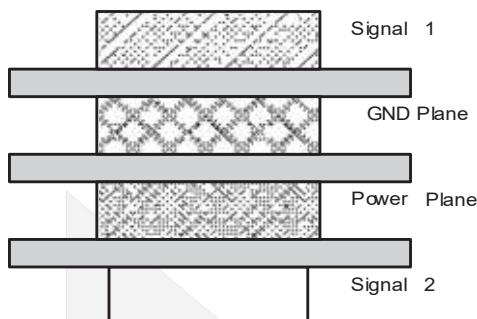

9. Due to the high frequencies associated with the USB, a printed circuit board with at least four layers is recommended; two signal layers separated by a ground and power layer as shown in Figure 17.

**Figure 17. Four-layer board stack-up**

The majority of signal traces must run on a single layer, preferably Signal 1. Immediately next to this layer must be the GND plane, which is solid with no cuts. Avoid running signal traces across a split in the ground or power plane. When running across split planes is unavoidable, sufficient decoupling must be used. Minimizing the number of signal vias reduces EMI by reducing inductance at high frequencies.

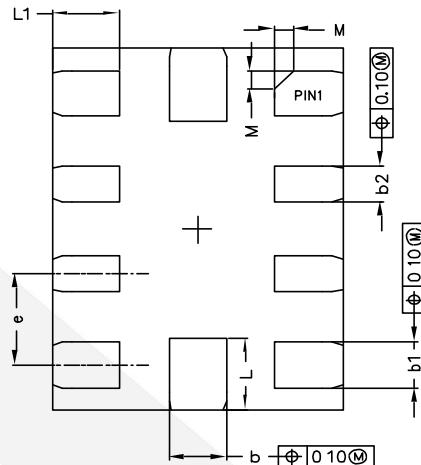

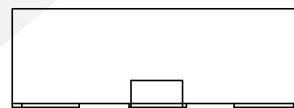

## Physical Dimensions: QFN2\*1.5-10

TOP VIEW

SIDE VIEW

SIDE VIEW

| Common Dimensions<br>(Units of measure = Millimeter) |      |      |      |

|------------------------------------------------------|------|------|------|

| Symbol                                               | Min  | Nom  | Max  |

| A                                                    | 0.50 | 0.55 | 0.60 |

| A1                                                   | 0    | 0.02 | 0.05 |

| (A3) 0.152 REF                                       |      |      |      |

| b                                                    | 0.25 | 0.30 | 0.35 |

| b1                                                   | 0.20 | 0.25 | 0.30 |

| b2                                                   | 0.15 | 0.20 | 0.25 |

| D                                                    | 1.45 | 1.50 | 1.55 |

| E                                                    | 1.95 | 2.00 | 2.05 |

| e                                                    | 0.40 | 0.50 | 0.60 |

| L                                                    | 0.35 | 0.40 | 0.45 |

| L1                                                   | 0.30 | 0.35 | 0.40 |

| M 0.10 REF                                           |      |      |      |

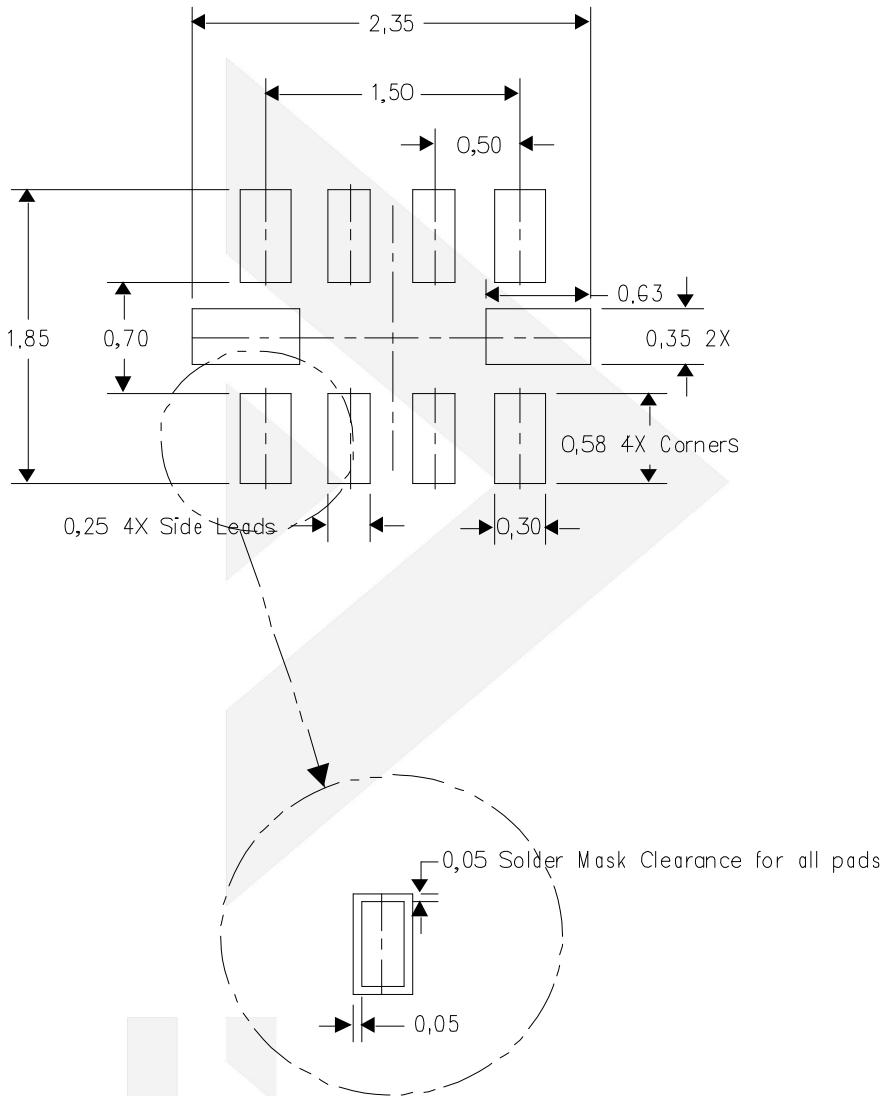

## Example Board Layout

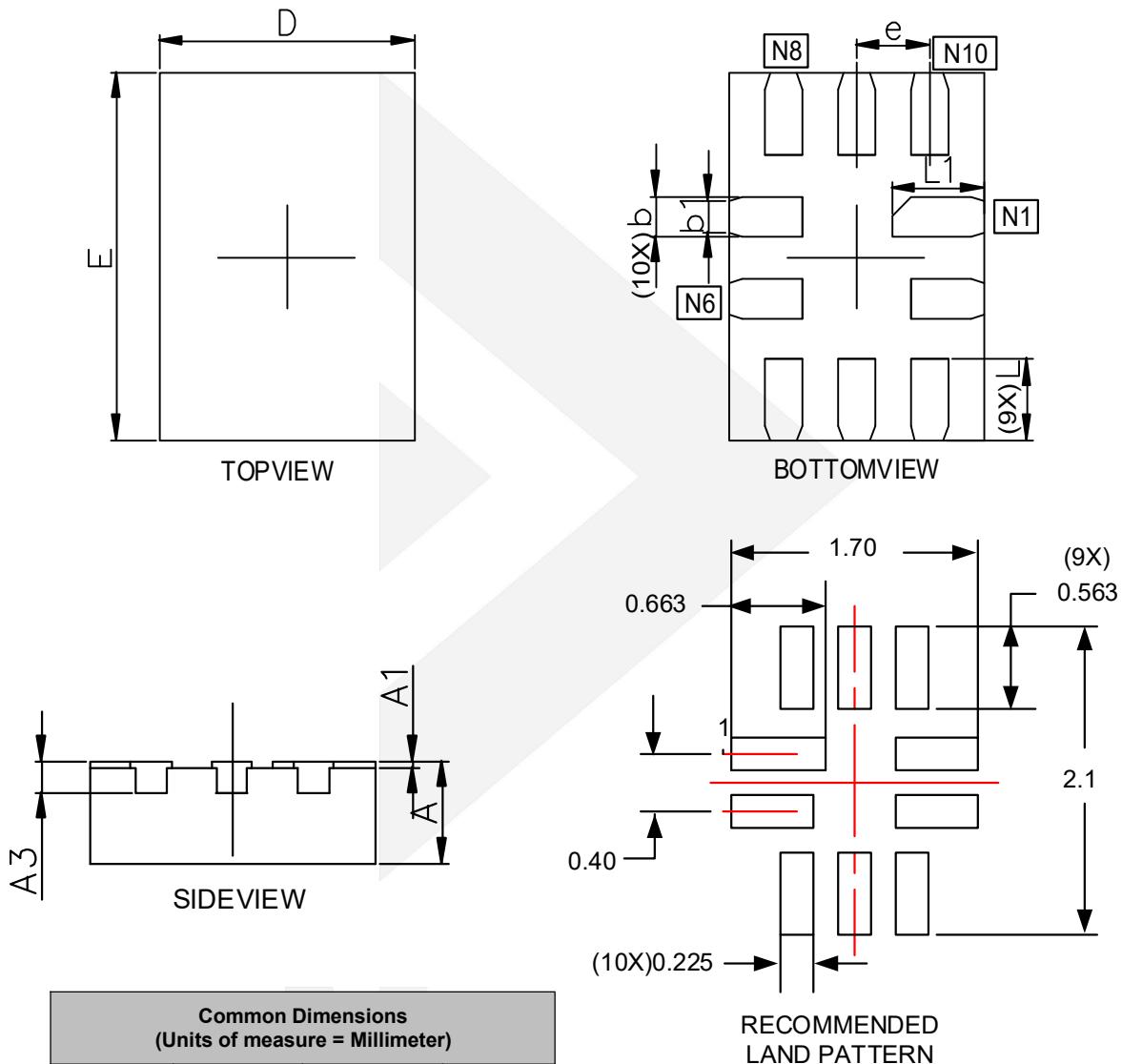

**Physical Dimensions: DQFN1.8\*1.4-10**

| Common Dimensions<br>(Units of measure = Millimeter) |           |     |      |

|------------------------------------------------------|-----------|-----|------|

| Symbol                                               | Min       | Nom | Max  |

| A                                                    | 0.50      | -   | 0.6  |

| A1                                                   | 0         | -   | 0.05 |

| A3                                                   | 0.152 REF |     |      |

| D                                                    | 1.35      | -   | 1.45 |

| E                                                    | 1.75      | -   | 1.85 |

| D1                                                   | -         | -   | -    |

| E1                                                   | -         | -   | -    |

| k                                                    | -         |     |      |

| b                                                    | 0.15      | -   | 0.25 |

| b1                                                   | 0.10      | -   | 0.20 |

| e                                                    | 0.40TYP   |     |      |

| L                                                    | 0.35      | -   | 0.45 |

| L1                                                   | 0.45      | -   | 0.55 |

DIO5008

DP/DM Dual-SPDT Switch with 20 V Overvoltage Protection

## CONTACT US

Dioo is a professional design and sales corporation for high-quality and performance analog semiconductors. The company focuses on industry markets, such as, cell phone, handheld products, laptop, and medical equipment and so on. Dioo's product families include analog signal processing and amplifying, LED drivers and charger IC. Go to <http://www.dioo.com> for a complete list of Dioo product families.

For additional product information, or full datasheet, please contact with our Sales Department or Representatives.